原文链接

一、下载源码

tinyriscv 官方库链接:https://gitee.com/liangkangnan/tinyriscv

这里我选择的是 master v2.4 版本: https://gitee.com/liangkangnan/tinyriscv/tree/v2.4/

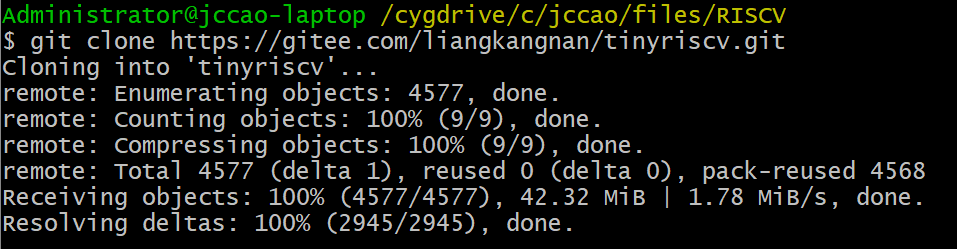

用 Git 克隆到本地。(使用的终端软件是 Cygwin,

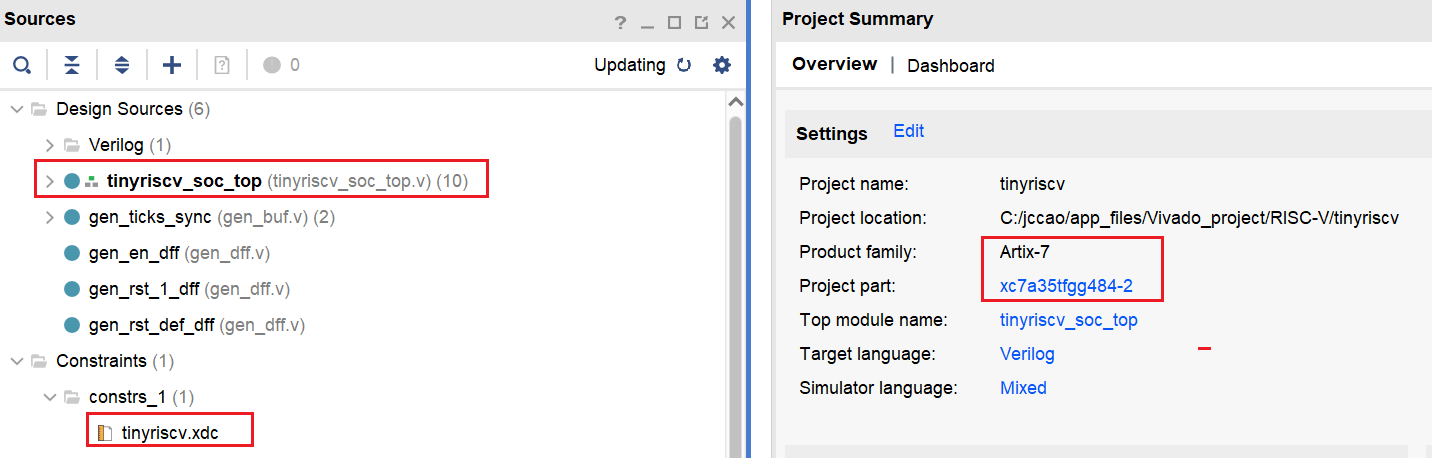

二、创建 Vivado 工程

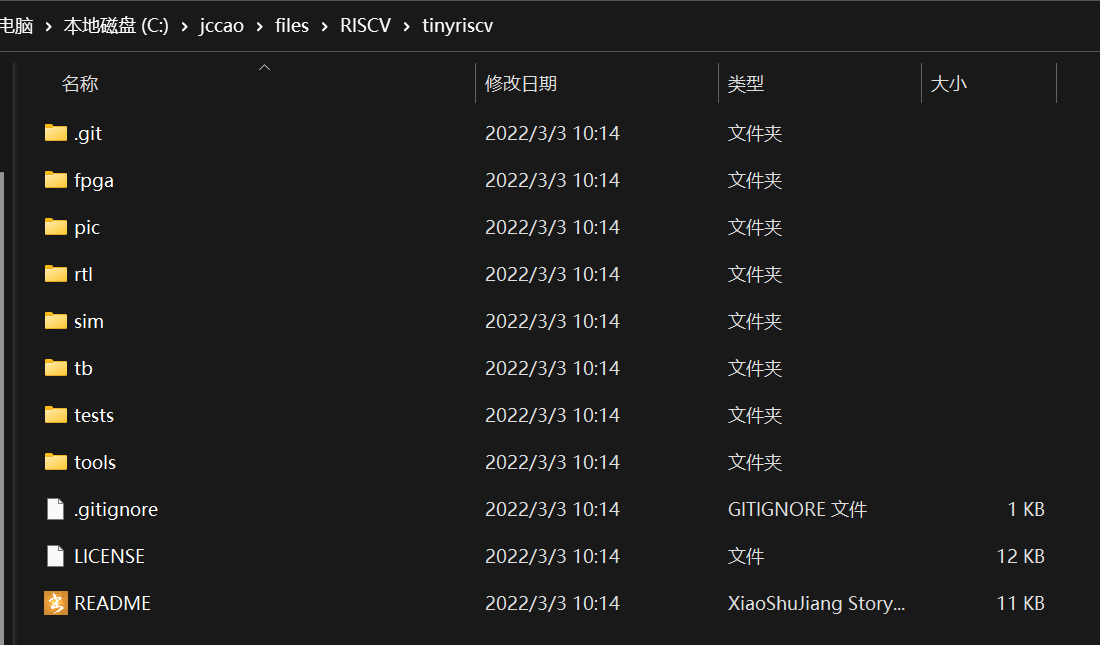

打开 tinyriscv 文件夹,可以看到有很多目录:

这里 rtl 为tinyriscv Verilog源码。

用 Vivado 创建工程,并把源码和约束添加进去,具体步骤可见 tinyriscv\fpga\README.md 文件,写的很详细。

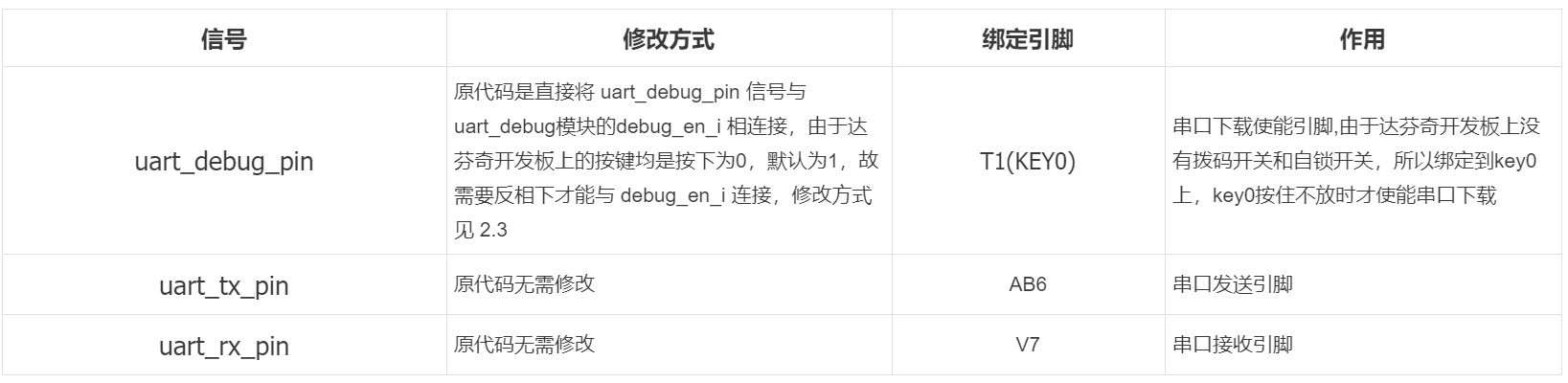

三、修改约束文件

所谓的移植其实就是根据自己所用的板卡编写正确的管脚约束文件,并且根据需求修改源码。

基本步骤如下:先修改约束文件中的时钟和复位引脚绑定

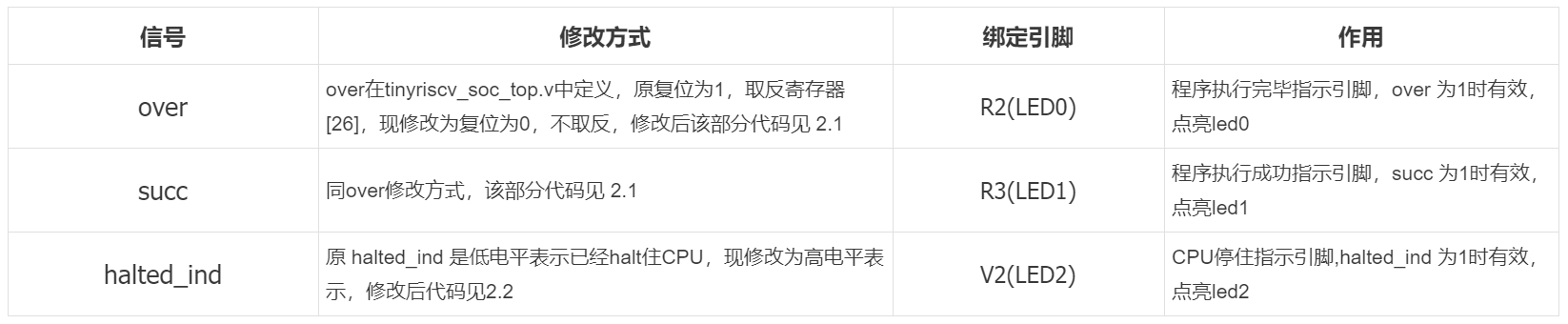

修改状态指示信号引脚绑定

在源码中,over、succ、halted_ind都是状态指示信号,应该绑定到开发板上的 LED上,而不同的开发板LED的电路连接方式也不同,有的是给高电平亮,有的是给低电平亮。而 tinyriscv 源码中是给低电平,即状态指示信号有效时为低电平,而达芬奇开发板LED是要给高电平亮,所以要修改源码,取反下就行。

3.修改串口 tx 和 rx 信号引脚绑定

注:这个是绑开发板中未使用的任意管脚,而不是绑开发板上已有的串口。

4.修改GPIO外设所用的引脚约束

5.修改JTAG所用的引脚约束注:这个是绑开发板中未使用的任意管脚,而不是绑FPGA自己的JTAG,FPGA自己的JTAG已经和开发板上的Flash绑定好了,无法使用,就像按键,led灯所绑定的管脚一样,都已经被使用了,无法被复用。

6.修改SPI所用的引脚约束

7.添加时钟约束

由于 jtag_TCK 信号在设计中是作为同步时钟的,而敏感列表中无晶振时钟所对应的信号。所以要添加下面语句;

create_clock -name jtag_clk_pin -period 300 [get_ports {jtag_TCK}];

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK]完整的约束文件:

# 时钟约束50MHz,占空比50%

create_clock -add -name sys_clk_pin -period 20.00 -waveform {0 10} [get_ports {clk}];

# 时钟引脚

set_property -dict { PACKAGE_PIN R4 IOSTANDARD LVCMOS33 } [get_ports {clk}];

# 复位引脚

set_property -dict { PACKAGE_PIN U2 IOSTANDARD LVCMOS33 } [get_ports {rst}];

# 程序执行完毕指示引脚,over 为1时有效,点亮led0

set_property -dict { PACKAGE_PIN R2 IOSTANDARD LVCMOS33 } [get_ports {over}];

# 程序执行成功指示引脚,succ 为1时有效,点亮led1

set_property -dict { PACKAGE_PIN R3 IOSTANDARD LVCMOS33 } [get_ports {succ}];

# CPU停住指示引脚,halted_ind 为1时有效,点亮led2

set_property -dict { PACKAGE_PIN V2 IOSTANDARD LVCMOS33 } [get_ports {halted_ind}];

# 串口下载使能引脚,由于没有拨码开关和自锁开关,所以绑定到key0上,key0按住不放时才使能串口下载

set_property -dict { PACKAGE_PIN T1 IOSTANDARD LVCMOS33 } [get_ports {uart_debug_pin}];

# 串口发送引脚

set_property -dict { PACKAGE_PIN AB6 IOSTANDARD LVCMOS33 } [get_ports {uart_tx_pin}];

# 串口接收引脚

set_property -dict { PACKAGE_PIN V7 IOSTANDARD LVCMOS33 } [get_ports {uart_rx_pin}];

# GPIO0引脚

set_property -dict { PACKAGE_PIN F16 IOSTANDARD LVCMOS33 } [get_ports {gpio[0]}];

# GPIO1引脚

set_property -dict { PACKAGE_PIN F15 IOSTANDARD LVCMOS33 } [get_ports {gpio[1]}];

# JTAG TCK引脚 PortA 0

set_property -dict { PACKAGE_PIN AA8 IOSTANDARD LVCMOS33 } [get_ports {jtag_TCK}];

create_clock -name jtag_clk_pin -period 300 [get_ports {jtag_TCK}];

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK]

# JTAG TMS引脚 PortA 3

set_property -dict { PACKAGE_PIN AB8 IOSTANDARD LVCMOS33 } [get_ports jtag_TMS];

# JTAG TDI引脚 PortA 1

set_property -dict { PACKAGE_PIN Y7 IOSTANDARD LVCMOS33 } [get_ports {jtag_TDI}];

# JTAG TDO引脚 PortA 2

set_property -dict { PACKAGE_PIN Y8 IOSTANDARD LVCMOS33 } [get_ports jtag_TDO];

# SPI MISO引脚

set_property -dict { PACKAGE_PIN F14 IOSTANDARD LVCMOS33 } [get_ports {spi_miso}];

# SPI MOSI引脚

set_property -dict { PACKAGE_PIN F13 IOSTANDARD LVCMOS33 } [get_ports {spi_mosi}];

# SPI SS引脚

set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports {spi_ss}];

# SPI CLK引脚

set_property -dict { PACKAGE_PIN E14 IOSTANDARD LVCMOS33 } [get_ports {spi_clk}];

#SPI 相关设置

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]

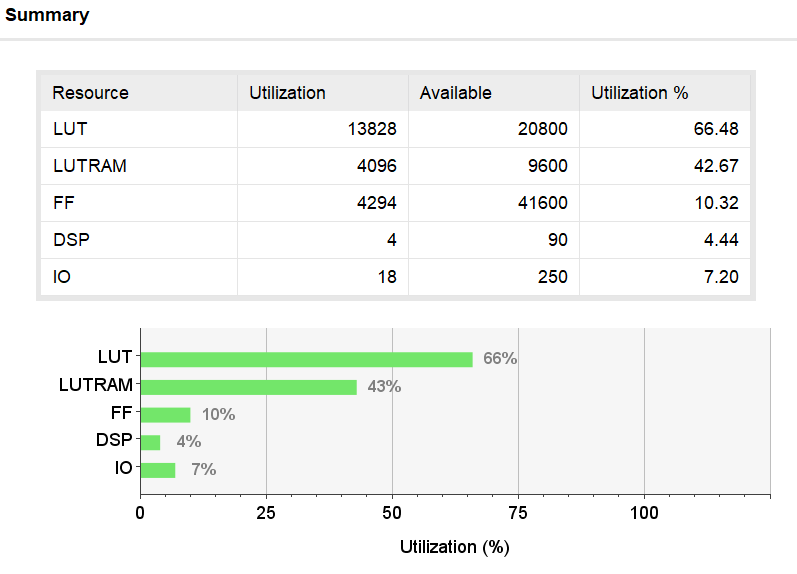

四、综合实现

Layout:

资源消耗;

所以只要板卡上的资源足够,都可以成功移植 tinyriscv。

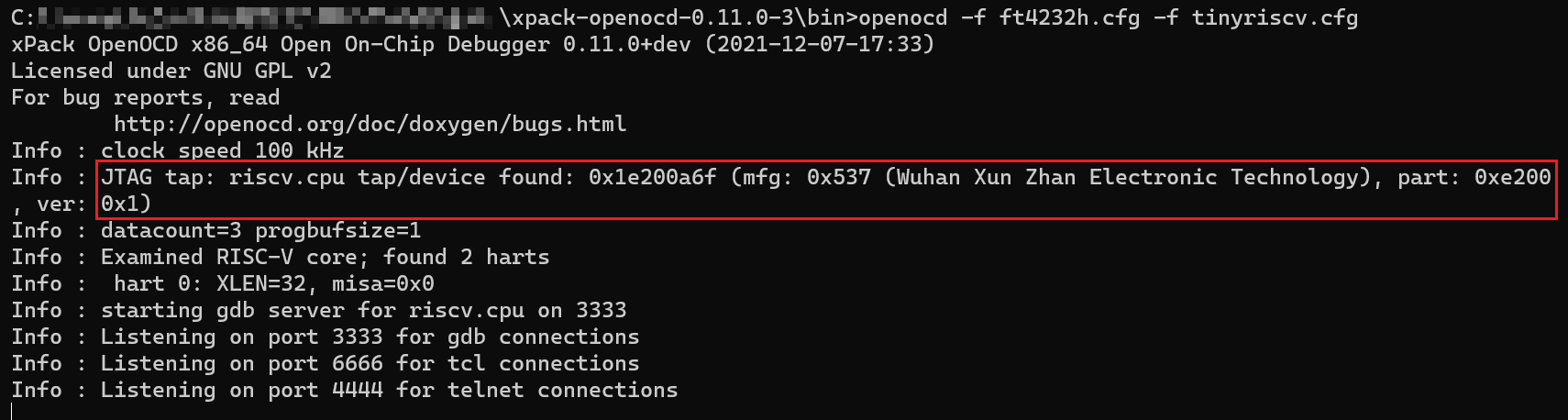

五、通过 JTAG debug RISCV

调试器芯片:ftdi4232HL

配置文件:

ft4232h.cfg:

adapter driver ftdi

# VID and PID

ftdi vid_pid 0x0403 0x6011

transport select jtag

# TCK frequency

adapter speed 100

# ftdi_layout_init [data] [direction]

# 指定FTDI GPIO的初始数据和方向,16bit数据宽度。

# 参数data中1表示高电平,0表示低电平,而参数direction中1表示输出,0表示输入(注意与常规的设定不同)

ftdi layout_init 0x0018 0x05fb

# ftdi_layout_signal name [-data|-ndata data_mask] [-input|-ninput input_mask] [-oe|-noe oe_mask] [-alias|-nalias name]

# 创建一个名字为name的信号。

# [-data|-ndata data_mask]

# data_mask:pin mask ndata:invert -data:normal bit

# data_mask是对应pin脚的掩码,-ndata表示输入数据反向,-data则不反向。

ftdi layout_signal nSRST -data 0x0010 -noe 0x0400

tinyriscv.cfg:

set _CHIPNAME riscv

jtag newtap $_CHIPNAME cpu -irlen 5 -expected-id 0x1e200a6f

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME riscv -chain-position $_TARGETNAME

riscv set_reset_timeout_sec 1

init

halt

打开 cmd 执行命令:openocd -f ft4232h.cfg -f tinyriscv.cfg

成功检测到 RISCV CPU。

原文链接