文章目录

- 28.1 VIRTUAL PROCESSOR IDENTIFIERS (VPIDS)

- 28.2 THE EXTENDED PAGE TABLE MECHANISM (EPT)

- 28.2.1 EPT Overview

- 28.2.2 EPT Translation Mechanism

- 28.2.3 EPT-Induced VM Exits

- 28.2.3.1 EPT Misconfigurations

- 28.2.3.2 EPT Violations

- 28.2.3.3 Prioritization of EPT Misconfigurations and EPT Violations

- 28.2.4 Sub-page Write Permissions

- 28.2.4.1 Write Access That Are Eligible for Sub-Page Write Permissions

- 28.2.4.2 Determining an Access's Sub-Page Write Permission

- 28.2.5 Accessed and Dirty Flags for EPT

- 28.2.6 Page-Modification Logging

- 28.2.7 EPT and Memory Typing

- 28.2.7.1 Memory Type Used for Accessing EPT Paging Structures

- 27.2.7.2 Memory Type Used for Translated Guest-Physical Addresses

- 28.3 **CACHING TRANSLATION INFORMATION**

- 28.3.1 Information That May Be Cached

- 28.3.2 Creating and Using Cached Translation Information

- 28.3.3 Invalidating Cached Translation Information

- 28.3.3.1 Operations that Invalidate Cached Mappings

- 28.3.3.2 Operations that Need Not Invalidate Cached Mappings

- 28.3.3.3 Guidelines for Use of the INVVPID Instruction

- 28.3.3.4 Guidelines for Use of the INVEPT Instruction

参考资料:

- intel EPT 机制详解

VMX 关于地址转换支持:VPID、EPT;Caching

第一段:

VMX: virtual-processor identifiers(VPIDs) 和 extended page-table(EPT)

- VMX 操作包含了 virtual-processor identifiers(VPIDS) 和 extended page-table(EPT)。

- VPIDs 是一种管理线性地址转换的机制。

- EPT 定义了一个地址转换层,进一步完善了地址转换过程。

第二段:

- Section 28.1。详细介绍了 VPIDs 的结构。

- Section 28.2。详细介绍了 EPT。

- Section 28.3。逻辑处理器如何缓存来自分页结构的信息、如何使用缓存的信息、软件如何管理缓存的信息。

28.1 VIRTUAL PROCESSOR IDENTIFIERS (VPIDS)

第一段:

传统方式需要 VMX 转换的形式来强制刷新 TLBs 和分页结构缓存。

- 传统 VMX 操作是需要通过 VMX transitions 来刷新 TLBs 和 paging-structure caches。

- 传统方式确保了旧的缓存信息在分页过程结束后不会再使用。

第二段:

VPIDs:能够帮助缓存多个线性地址空间信息,逻辑处理器可以任意切换到不同的线性地址空间。

- VPIDs 为 VMX 操作引入了一种工具,通过这种工具,逻辑处理器可以缓存多个线性地址空间的信息。

- 使用 VPIDs 时,VMX transitions 可能会保留缓存的信息,逻辑处理器会切换到不同的线性地址空间。

第三段:

lcpu 使用 16-bit 的 VPID 来标记不同的缓存内容。

VPID 的取值。

Section 28.3 说明了逻辑处理器如何管理缓存在多个线性地址空间的信息。逻辑处理器可以使用 16-bit 的 VPID 来标记一些缓存的信息。以下规定了如何在任何时候确定当前的 VPID:

- 在以下情况下,VPID=0000H:

- Outside VMX operation。(这包括在系统管理模式下的操作,默认情况下使用 VMX 操作对 SMIs 和 SMM 进行处理,Section 34.14)

- VMX root operation。

- 当“enable EPT” VM-exection control 为 0时,VMX non-root operation。

- 如果逻辑处理器在 VMX non-root operation 下,并且当“enable EPT” VM-exection control 为 1,当前 VPID 的值为 VMCS 中 VM-excution control 字段(field)中的 VPID 值。(VM entry 确保 VPID 的值不会是 0000H,Section 26.2.1)。

第四段:

当 VPID(virtual-processor identifiers) 和 PCID(process-context identifiers) 二者被处理器相关联时,二者可以同时使用。

- VPIDs 和 PCIDs(Section 4.10.1)可以同时使用。

- **当二者同时使用时,处理器将缓存的信息与 VPID 和 PCID 相关联。**仅当前 VPID 和 PCID 都与缓存信息相关联时,才使用缓存信息。

28.2 THE EXTENDED PAGE TABLE MECHANISM (EPT)

第一段:

将 Guest-physical addresses 进一步通过 EPT 分页结构转换为 Host-physical-address(HPA),达到最终访问内存的目的。

GPA --EPT paging structures–> HPA

- extended page-table mechanism(EPT,扩展页表机制)是一种可用于支持物理内存虚拟化的功能。

- 当使用 EPT 时,某些通常被视为物理地址(用于访问内存)的地址被视为 Guest-physical addresses(GPA)。

- Guest-physical addresses(GPA) 通过遍历一组 EPT paging structures 来进行地址转换,以产生用于访问实际物理内存的地址。

- Section 28.2.1 Overview of EPT。

- Section 28.2.2 描述了基于 EPT 的地址转换的操作。

- Section 28.2.3 讨论了由 EPT 引发的 VM exits 情况。

- Section 28.2.7 EPT 和 内存类型之间的联系。

28.2.1 EPT Overview

第一段:

"enable EPT" VM-exection control=1,EPT 开启。

EPT 在 VMX 非根模式下转换 GPA。

- 当 “enable EPT” VM-exection control 为 1,EPT 启用。

- EPT 在 VMX non-root operation 下转换 guest-physical address(GPA),并且这些地址在 VM entry 时用于事件注入(event injection)。

第二段:

EPT 分页结构类似于 4-level 模式下的分页结构。

- 从 guest-physical addresses(GPA) 到 physical addresses(HPA) 的地址转换取决于一组 EPT paging structures。

- EPT paging structures 类似于 IA-32e 模式时用的线性地址转换结构。

- Section 28.2.2 详细介绍了 EPT 分页结构。

第三段:

当 CR0.PG=1 & “enable EPT” VM-exection control 为 1 时,分页结构为 guest paging-structures。

如果 CR0.PG=0,无 guest paging structures,所有线性地址均为 GPA,可能也会通过 EPT 进行转换。

- 如果 CR0.PG=1,线性地址的转换会使用到 CR3 寄存器(开启分页)。

- 当 “enable EPT” VM-exection control 为 1,分页转换结构被称为 guest paging structures。

- 如果 CR0.PG=0,无 guest paging structures,所有线性地址均为 guest-physical address(GPA),可能也会通过 EPT 进行转换。

第四段:

“enable EPT” VM-exection control=1 & CR0.PG=1,说明线性地址转换还未完毕,还需要借助 EPT 继续寻找真实物理地址。

当 “enable EPT” VM-exection control 为 1,是否为 guest-physical addresses,取决于 CR0.PG:

- 如果 CR0.PG=0,所有线性地址均为 guest-physical address(GPA)。

- 如果 CR0.PG=1,GPA 来自寄存器 CR3 的内容和 guest paging structures 的内容。(这包括逻辑处理器存储在内部非架构寄存器中的 PDPTEs 的值),后者包括(在 PT 项和其它分页结构项中,第 7 位(PS)为1(映射大页))由 guest paging structures 转换的线性地址。

第五段:

32-bit 4KB 举例。

GVA – guest paging structures --> GPA – EPT --> HPA

CR3 中存放高端起始地址的 GPA。

如果 CR0.PG=1,线性地址到物理地址的转换需要使用 EPT 来对 GPA 进行多次转换。例如,假设 CR4.PAE=CR4.PSE=0(4KB 页面),32-bit 线性地址的转换操作如下:

- 【10bit】31:22-选择起始物理地址(guest-physical address)存放在 CR3 中的 guest page directory 中的一项。guest PDE 的 guest-physical address 通过 EPT 来确定 guest PDE 的 physical address。

- 【10bit】21:12-选择存放在 guest PDE 中的 guest page table 的 guest-physical address。EPT 将 PTE 的 guest-physical address 转换成 PTE 的 physical address。

- 【12bit】11:0-guest PTE 中存放的物理地址为 guest-physical 页框的页内偏移。EPT 将 guest-physical address 转换为 physical address。

第六段:

EPT 还能够指定访问内存时的权限,不允许的访问称为 EPT violations,这将会导致 VM exits。

除了能够将 guest-physical address(GPA) 转换为 host-physical address(HPA),EPT 还指定了软件在访问地址时的权限。不允许的访问被称为 EPT violations,并会导致 VM exits,See Section 28.2.3。

第七段:

- GPA 在访问内存时,才用 EPT 来转换成物理地址。

- PAE 分页模式下,MOV(GPA) to CR3, 将 PDPTEs 的 GPA 加载。

- MOV to CR0/CR4,CR3 被重新加载(PDPTEs 发生了变化)。

- 加载 PDPTEs(GPA) 的指令由于不会访问物理内存,故不会使用 EPT 进行地址转换,只有在用到 PDPTEs 进行地址转换时,才会通过 EPT 访问内存。

处理器仅在 guest-physical address(GPA) 被用来访问内存时,才用 EPT 来转换这些物理地址。这一原则包含以下内容:

- MOV to CR3 会导致 CR3 重新加载 guest-physical address(GPA)。该地址是否通过 EPT 转换取决于是否使用 PAE 分页模式。

- 如果 PAE 分页模式未被使用,指令(MOV to CR3)不会使用该地址来访问内存,也不会通过 EPT 对其进行转换。(如果 CR0.PG=1,地址将在下一次使用线性地址访问内存时通过 EPT 进行转换)

- 如果 PAE 分页模式使用,指令会从 guest-physical address(GPA) 所对应的地址处加载四个 PDPTEs,并且会通过 EPT 进行地址转换。

- Section 4.4.1 确定了 MOV to CR0 和 MOV to CR4 的执行,会导致来自 guest-physical address 的 PDPTEs 重新加载到 CR3。这两种执行会导致使用 EPT 转换 guest-physical address 地址。(CR0.CD、CR0.PG、CR4.PAE…)

- PDPTEs 包含了 guest-physical address,加载 PDPTEs 的指令不使用 guest-physical address 来访问内存,也不会导致它们通过 EPT 进行转换。PDPTE 中的 guest-physical address 将会在下一次内存访问时通过 EPT 使用该 PDPTE 的线性地址进行转换。

28.2.2 EPT Translation Mechanism

第一段:

EPT 针对 48 bit 的 GPA 进行转换。

EPT 通过 4 个分页结构项进行转换。

- EPT 转换使用 guest-physical address[47:0]。

- 它使用的 page-walk 长度为 4(页表个数),这意味着最多可以访问 4 个 EPT paging-structure 项来转换一个 guest-physical address。

第二段:

逻辑处理器对这 48 位进行分段,以遍历 EPT paging-structure:

- 【EPT PML4】一个 4KB 对齐的 EPT PML4 表位于extended-page-table pointer(EPTP) 的位 51:12 中指定的物理地址字段——VM-excution control field(Table 24-8 in Section 24.6.11)。EPT PML4 table 包含了 512 个 64-bit 项,使用如下定义的物理地址来选择 EPT PML4E。即 EPTP 中保存的内容。

- Bits[63:52] 0.

- Bits[51:12] from EPTP.

- Bits[11:3] are bits[47:39] of guest-physical address.(9-bit)

- Bits[2:0] 0.(8B)

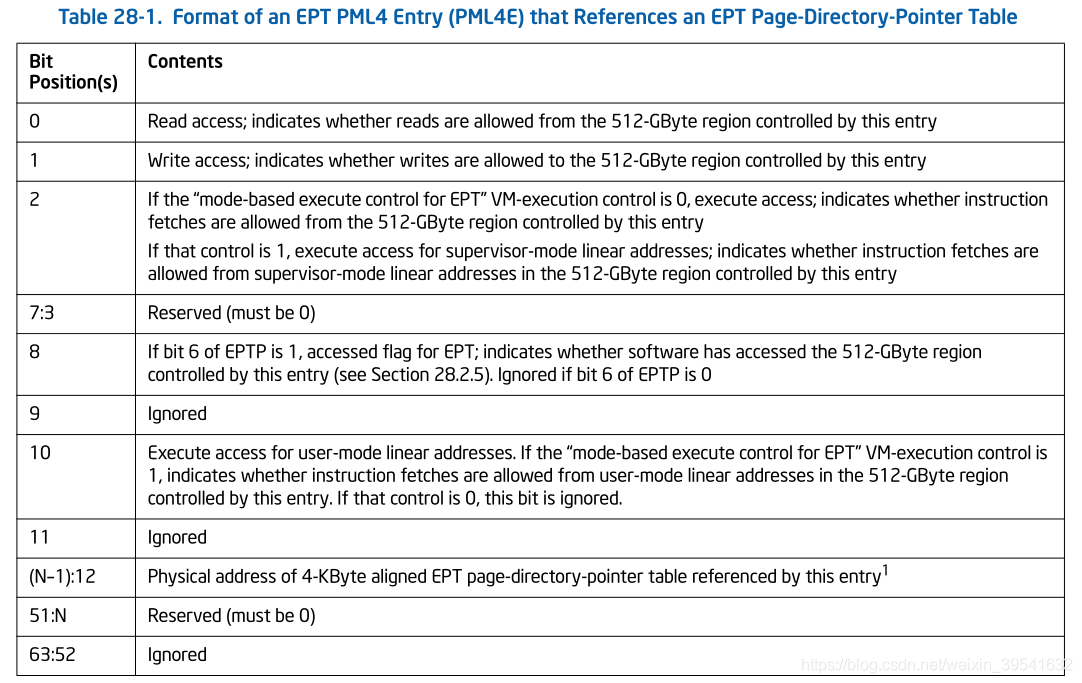

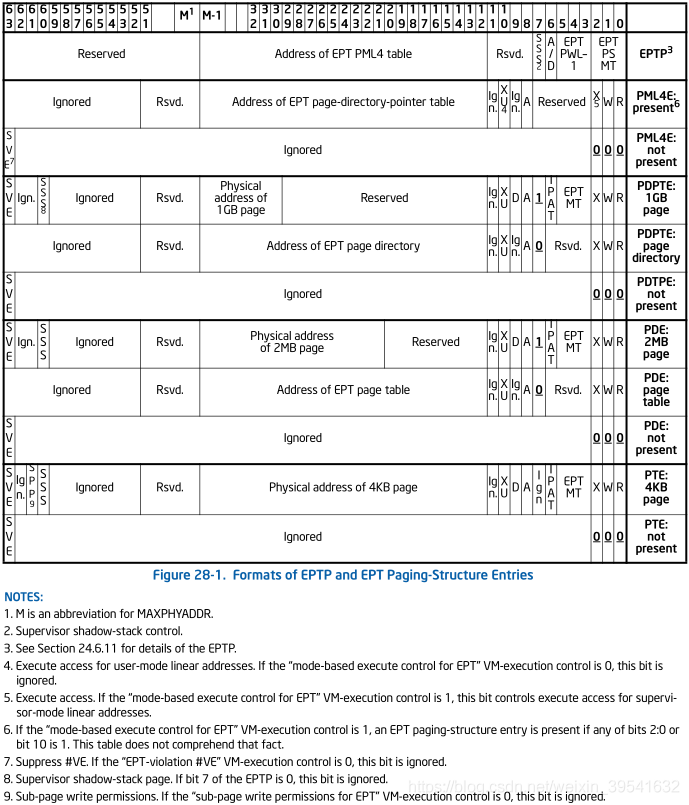

因为 EPT PML4E 是使用 guest-physical address[47:39] 标识的,所以它控制对 512GB guest-physical address 空间的访问。EPT PML4E 的格式如 Table 28-1。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-oLdInWrA-1607654219794)(C:\Users\jiaming\Desktop\Chapter 28.assets\IMG_20201101_123606-1605013281778.jpg)]

(N 是处理器支持的物理地址宽度。软件可以通过在 EAX 用 80000008H 执行 CPUID 来确定处理器的物理地址宽度。物理地址宽度以 EAX[7:0] 返回)

- 【EPT PDPT】一个 4KB 自然对齐的 EPT PDPT 位于 EPT PML4E[51:12] 所指定的物理地址中。EPT PDPT 包含了 512 个 64-bit 项。使用如下定义的物理地址来选择 EPT PDPTE:

- Bits[63:52] 0.

- Bits[51:12] from EPT PML4E.

- Bits[11:3] are bits[38:30] of guest-physical address.

- Bits[2:0] are 0.

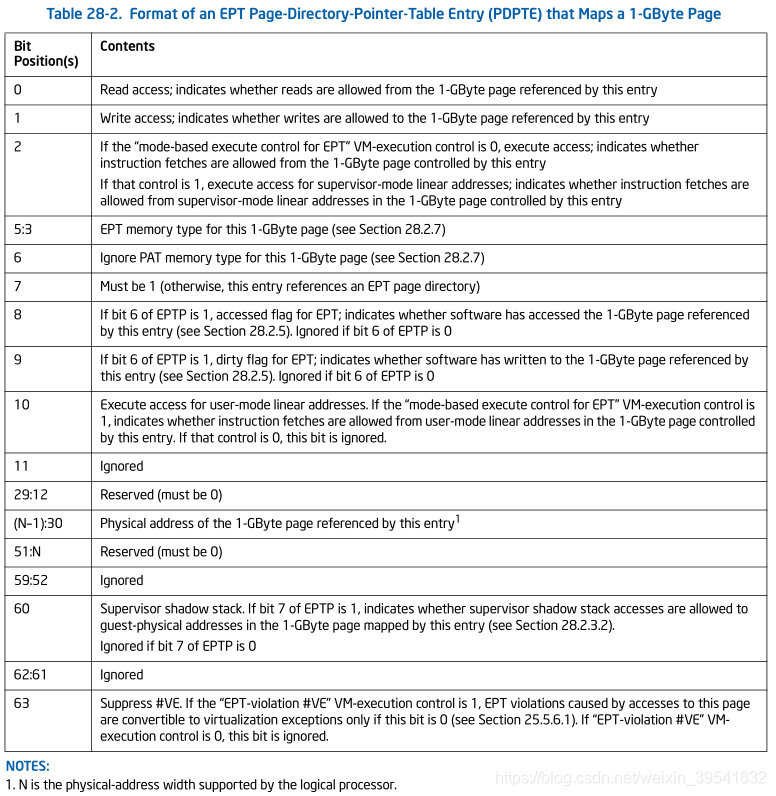

因为 EPT PDPTE 使用 guest-physical address[47:30]位来标识的,所以它控制对 1GB 的 guest-physical address 的访问。EPT PDPTE 的使用取决于该项位 7 的值:

- 【1GB-page】bits[7](EPT PDPTE)=1,EPT PDPTE 映射一个 1GB 页面。最终物理地址的计算如下:

- Bits[63:52] 0.

- Bits[51:30] from EPT PDPTE.

- Bits[29:0] original guest-physical address.(offest)

映射 1G 页面的 EPT PDPTE 的格式如 Table 28-2。

- EPT PDPTE.7=0,一个 4KB 自然对齐的 EPT PD 位于 EPT PDPTE 的位 51:12 中指定的物理地址。映射 EPT PD 的 EPT PDPTE 的格式如 Table 28-3。

- 【EPT PD】EPT PD 包含了 512 个 64-bit PDE,使用如下定义的物理地址来选择一个 EPT PDE:

- Bit[63:52] 0

- Bits[51:12] from EPT PDPTE.

- Bits[11:3] are guest-physical address[29:21].

- Bits[2:0] 0.

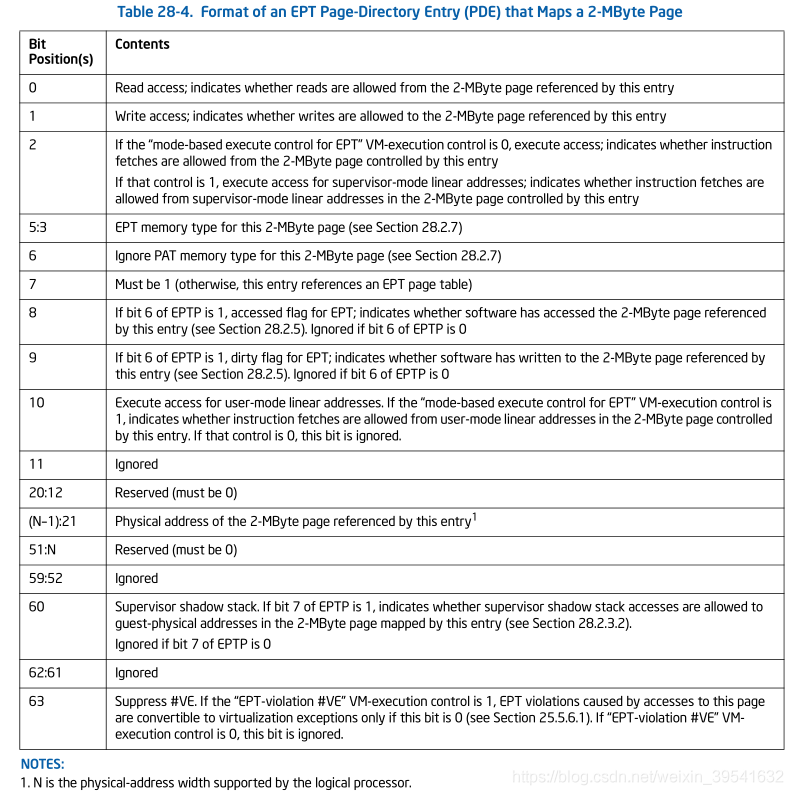

因为 EPT PDE 是使用 guest-physical address[47:21] 位来标识的,所以它控制对 guest-physical address 空间的 2MB 访问。EPT PDE 的使用取决于该项的第 7 位:

- 【2MB-page】如果 EPT PDE[7]=1,EPT PDE 映射 2MB 页(Table 28-4),最终页面物理地址构成:

- Bits[63:52] 0.

- Bits[51:21] from EPT PDE.

- Bits[20:0] from guest-physical address.

- EPT PDE.7=0,4KB 自然对齐的 EPT PT 位于 EPT PDE[51:12] 中指定的物理地址,映射 EPT PT 的 EPT PDE 格式如 Table 28-5 所示。

- 【EPT PT】EPT PT 包含 512 个 64-bit 项,将每个 EPT PTE 的物理地址做如下划分:

- Bits[63:52] 0.

- Bits[51:12] from EPT PDE.

- Bits[11:3] are gust-physical address[20:12].

- Bits[2:0] 0

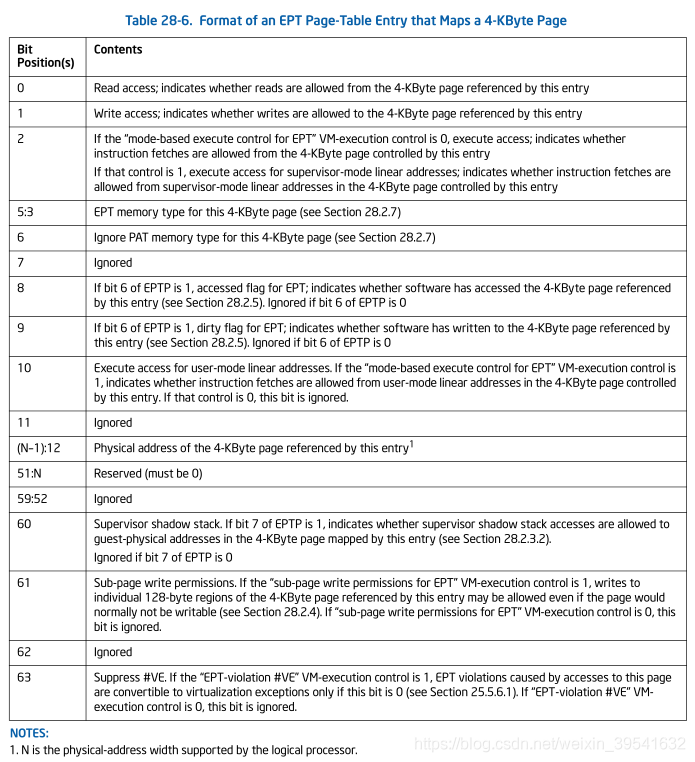

- 【4KB-page】因为 EPT PTE 使用 guest-physical address[47:12],故每个 EPT PTE 映射 4KB 页面,最终 4KB 页面物理地址构成(Table 28-6):

- Bits[63:52] 0.

- Bits[51:12] from EPT PTE.

- Bits[11:0] from guest-physical address.

如果 EPT paging-structure 项中位[2:0]中任何一位为 1,则 EPT paging-structure 项存在。

对 GPA 的转换,如果遇到不存在的 EPT paging structure 将会导致 EPT violation。

If the “EPT-violation #VE” VM-execution control is 1 & EPT paging-structure[63]=0,EPT violation 转换为虚拟化异常,否则,当字段为 0 时,忽略第 63 位。

- 如果 EPT paging-structure 项中位[2:0]中任何一位为 1,则 EPT paging-structure 项存在。

- 处理器忽略位[62:3],既不使用该项映射另一个 EPT paging-structure 项,也不产生物理地址。

- 对 GPA 的转换,如果遇到不存在的 EPT paging structure 将会导致 EPT violation(Section 28.2.3.2)

- If the “EPT-violation #VE” VM-execution control is 1, the EPT violation is convertible to a virtualization exception only if bit 63 is 0; see Section 25.5.6.1. (仅当位 63 为 0 时,EPT violation 才可转换为虚拟化异常)

- If the “EPT-violation #VE” VM-execution control is 0, this bit is ignored.(位 63)

NOTE

If “mode-based execute control for EPT” VM-execution control is 1 时,如果 EPT paging-structure bit 2:0 或 bit 10 中的任何一位为 1,则存在 EPT paging-structure。If bit 2:0 全部为 0,bit 10 is 1,则该项通常用于映射另一个 EPT paging-structure 或产生一个物理地址。

- If “mode-based execute control for EPT” VM-execution control is 1,如果 EPT paging-structure bit 2:0 或 bit 10 中的任何一位为 1,则存在 EPT paging-structure,If bit 2:0 全部为 0,bit 10 is 1,则该项通常用于映射另一个 EPT paging-structure 或产生一个物理地址。

- 上面讨论描述了 EPT paging-structure 如何相互映射,以及逻辑处理器在转换 GPA 时如何遍历这些结构。

- EPT paging-structure 没有涵盖页面映射过程的所有细节,其它细节如下:

- Section 28.2.3 描述了页面转换过程可能导致 VM exits。

- Section 28.2.7 描述了 EPT translation 机制和内存类型之间的联系。

- Figure 28-1 给出了 EPTP 和 EPT paging-structure 项的概要。对每个 EPT paging-structure,它分别标识页面的项的格式,映射其它 EPT pagin-structure,以及因为不存在而两者都不映射的项;位 2:0 和位 7 被突出显示,因为它们决定了使用怎样的 paging-structure。(Figure 28-1 没有表现这样一个事实,如果“mode-based execute control for EPT” VM-execution control 为 1,位 2:0 或位 10 中的任何一位为 1,则存在一个项。)

28.2.3 EPT-Induced VM Exits

第一段:

GPA 转换过程中会产生 EPT misconfiguration(EPT 分页结构项中含有未知值)、EPT violations(没有前者发生,但是GVA不允许访问) 和 page-modification log-full(log 满),这些会导致 VM exits。

- 使用 GPA 可能会导致虚拟机因 EPT misconfiguration、EPT violations 和 page-modification log-full 而 VM exits。

- 当逻辑处理器在转换一个 GPA 时,遇到一个 EPT paging structure 项中包含有一个未知的值的时候, 就会发生 EPT misconfiguration。

- 当没有发生 EPT misconfiguration,但是 EPT paging-structure 项不允许 guest-address 访问,就会发生 EPT violation。(Section 28.2.3.2)

- pag-modification log-full event 发生在逻辑处理器需要创建 page-modification log 项,但是 log 已满。(Section 28.2.6)

第二段:

在进行 GPA 转换之前,仅可能会发生 page-modification log-full 错误。

- 这些事件发生在试图用 GPA 访问内存时。

- 用 MOV to CR3 加载带有 GPA 的 CR3,在该地址用于 paging-structure 之前,既不会导致 EPT configuration 也不会导致 EPT violation。

第三段:

If “EPT-violation #VE” VM-execution control is 1,某些 EPT violation 可能会导致虚拟化异常,而不是 VM exits。Section 25.5.6.1。

28.2.3.1 EPT Misconfigurations

发生此类异常的四种情况。

如果 GPA 转换时遇到满足下面任何条件的 EPT paging-structure,就会发生 EPT misconfiguration:

- EPT 项中的位 0 置零 (表示不允许数据读取),位 1 置位 (表示允许数据写入)。

- 如果处理器不支持excute-only translations:

- EPT 项的位 0 置零(表示不允许数据读取),位 2 置位 (表示允许指令读取)。

- “mode-based execute control for EPT” VM-execution control is 1,EPT 项的第 0 位置零 (表示不允许数据读取),位 10 置位(表示允许从用户模式线性地址提取指令)。

软件应该读取 VMX 相关 MSR IA32_VMX_EPT_VPID_CAP,以确定是否支持 execute-only translations。(Appendix A.10)

- EPT 页面结构项存在(Section 28.2.2),并且存在以下情况之一:

- 保留位被置位。这包括在逻辑处理器物理地址宽度之外的51:12范围内设置一个位。有关在哪个EPT paging-structure 项中保留哪些位的详细信息,请参见 Section 28.2.2。

- 该项的最后一个用于转换 guest-physical address(位 7 设置为 1 的 EPT PDE 或 EPT PTE),位 5:3(EPT 内存类型)的值是 2,3 或 7(这些值是保留的)。

- 当 EPT paging-structure 项置位了为将来功能保留的位时,就会导致 EPT misconfigurations。

- 软件开发人员应该意识到,将来可能会使用到这些位,并且导致一个处理器上的 EPT misconfigurations 的 EPT paging-structure 项并不会用到这些位。

28.2.3.2 EPT Violations

发生此类异常的 5 种情况。

在使用 GPA 访问的过程中,如果地址转换过程不会导致 EPT misconfiguration,则可能会发生 EPT violation。以下任何情况下都会发生 EPT violation:

- GPA 的映射时遇到了不存在 EPT paging-structure 项。(Section 28.2.2)。

- (EPT 分页结构项中的第 0 位为零时(不允许数据读取),访问该 EPT 分页结构)数据读取式访问,对于要读取的任何字节,在用于转换该字节的 GPA 的任何 EPT paging-structure 项中,位 0 (读取访问)被清零。由于 guest paging structures 逻辑处理器为转换线性地址而进行的读取被认为是数据读取。(针对 EPT 分页结构项中的位 0)

- (EPT 分页结构项中的第 1 位为零时(不允许数据写入),更改该 EPT 分页结构项中的内容)数据写入式访问,对于要写入的任何字节,位1(写访问)在用于转换该字节的 GPA 的任何 EPT paging-structure 中被清零,逻辑处理器写入 guest paging structures 以更新访问和脏标志被视为数据写入。如果 EPT 指针(EPTP)的第 6 位为 1 (启用 EPT 的已访问和脏标志),处理器对 guest paging structures 项的访问将被视为 EPT violations 写入。因此,如果在用于转换 GPA 的分页结构项的任何 EPT paging-structure 项中位 1 被清零,则试图使用该项来转换线性地址会导致 EPT violations。

(这不适用于 PAE 分页中使用 MOV to CR 指令加载 PDPTE 寄存器(并不访存);参见第4.4.1节。这些加载的 GPA 被视为读取,不会因 GPA 不可写而导致 EPT violations)

If the “sub-page write permissions for EPT” VM-execution control is 1,则在某些情况下,向 GPA 写入不会导致 EPT violations(如上所述)。如果 GPA 使用 4KB 的页面映射,并且用于映射页面的 EPT PTE 的位61(子页面写权限)是 1,则可以允许对某些 128B 的子页面进行写操作。详见第28.2.4节。 - 指令提取式访问,EPT paging-structures 防止对正在提取的任何字节的执行访问。这是否发生取决于“mode-based execute control for EPT” VM-execution control的设置:

- 如果为 0,如果用于转换字节的 GPA 的任何 EPT paging-structure 项中的位 2 (执行访问)被清零,则禁止从字节中提取指令。

- 如果为 1,则在下列任一情况下,禁止从字节中提取指令:

- 分页将字节的线性地址映射为 supervisor-mode address,在用于转换字节的 GPA 的任何 EPTpaging-structures 项中,位 2(supervisor-mode address 的执行访问) 置 0 时。

如果在至少一个控制线性地址转换的分页结构项中,U/S 标志(位2)为 0,则分页将线性地址映射为 supervisor-mode address。 - 分页将字节的线性地址映射为 user-mode address,在用于转换字节的 GPA 的任何 EPTpaging-structures 项中,位 10(用户模式线性地址的执行访问) 置 0 时。

如果控制线性地址转换的所有分页结构项中的 U/S 标志为 1,则分页会将线性地址映射为 user-mode address。如果分页被禁用(CR0.PG=0),每个线性地址都是 user-mode address。

- 如果启用了 supervisor shadow-stack control (通过设置 EPTP 的位 7),则是 supervisor shadow-stack 访问,如果存在以下任何情况,用于转换 GPA 的 EPT paging-structures 项不允许 supervisor shadow-stack 访问:

- EPT paging-structures 项中,位 0(读访问)是置 0 的。

- EPT paging-structures 项中,位 1(写访问)是置 0 的。(并不会禁止 shadow-stack 的读取和写入。)

- EPT paging-structures 项中,位60(supervisor-shadow stack 访问)置 0。

使用 supervisor shadow-stack control 和 supervisor-shadow stack 访问 EPT paging-structures 不影响其对其它的访问(包括 user shadow-stack 访问)。

28.2.3.3 Prioritization of EPT Misconfigurations and EPT Violations

EPT Misconfigurations and EPT Violations 二者的优先级。

第一段:

EPT 引发的 VM Exits 的优先级。

将线性地址转换为物理地址需要使用 EPT 对 GPA 进行一次或多次转换(参见第28.2.1节)。本节规定了 EPT 引发的 VM Exits 相对于彼此以及使用线性地址访问内存时可能遇到的其他事件的相对优先级。

第二段:

对于对 GPA 的访问,根据一个迭代过程来确定是发生了 EPT Misconfigurations 还是 EPT Violations:

EPT 转换过程中判断是 EPT Misconfigurations 还是 EPT Violations?

- 读取一个 EPT paging-structures 项(最初,这是一个EPT PML4 项):

- 如果该项不存在(见第28.2.2节),则 EPT Violations。

- 如果该项存在,但其内容未正确配置(参见第28.2.3.1节),则会发生 EPT Misconfigurations 。

- 如果该项存在并且其内容配置正确,则操作取决于该项是否引用另一个EPT paging-structures (是位 7 设置为1的 EPT PDE 还是 EPT PTE):

- 如果该项映射了另一个 EPT paging-structures 项,则对另一个 EPT paging-structures 执行步骤 1。

- 否则,该项用于产生最终物理地址;执行步骤2。

- 一旦最终物理地址被确定,由 EPT paging-structures 项中的内容确定特权级:

- 如果这些权限不允许访问 GPA (参见第28.2.3.2节),则会发生 EPT Violations。

- 如果这些权限允许访问 GPA,则使用最终物理地址访问内存。

如果 CR0.PG = 1 时,线性地址的转换也是一个迭代过程,处理器首先访问由 CR3 中转换 GPA 的 EPT paging-structures (或者,如果使用 PAE 分页,则访问 PDPTE 寄存器中的 GPA),然后访问由第一个 EPT paging-structures 中的项所映射的另一个 EPT paging-structures,等等。每个 GPA 本身都使用 EPT,可能会导致由 EPT 引发的 VM exits。以下详细说明了在此迭代过程中如何识别 page faults 和 EPT 引发的 VM exits:

page faults 还是 EPT Misconfigurations or EPT Violations?

- 试图访问具有 GPA 的 guest paging-structure 项(最初,CR3 或 PDPTE 寄存器中的地址)。

- 如果访问因 EPT Misconfigurations 和 EPT Violations 而失败(见上文),则会发生 EPT 引发的 VM exits。

- 如果访问没有导致 EPT-induced(引发) VM exits,则检查当前分页结构项中的第 0 位(P):

- 如果 P=0 或者置位了任何保留位,则会发生 page-fault。

- 如果 P=1 且没有置位任何保留位,取决于该项是否映射了另一个分页结构项(guest PDE 的 PS=1 还是guest PTE):

- 如果该项映射了另一个分页结构项;对另一个项执行步骤 1。

- 否则,该项用于产生最终的 GPA;执行步骤2。

- 一旦最终的 GPA 被确定,由 EPT paging-structures 项中的内容确定特权级:

- 如果这些权限不允许对线性地址的访问(例如,这是对只读页面的写入),则会发生 page faults。

- 如果这些权限允许对线性地址的访问,则会尝试访问最终 GPA 的内存:

- 如果访问因 EPT Misconfigurations 和 EPT Violations 而失败(见上文),则会发生 EPT-induced VM exits。

- 如果访问没有 EPT-induced VM exits,则使用最终物理地址(使用 EPT 对最终 GPA 的转换)来访问内存。

如果 CR0.PG=0 时,线性地址被视为 GPA,并使用 EPT 进行转换(见上文)。如果该过程完成时没有 EPT Misconfigurations 和 EPT Violations,它将生成一个物理地址,并确定 EPT structures 项所确定的权限。如果这些权限不允许访问物理地址(参见第28.2.3.2节),则会发生 EPT Violations,否则使用物理地址访问内存。

28.2.4 Sub-page Write Permissions

第一段:

子页访问权限不会局限于分页结构项所指向的页面大小,而是可以做的更小,粒度更小。

- Section 28.2.3.2 解释了 EPT 如何使用 EPT Violations 来加强 GPA 的访问权限。

- 这些访问权限是 EPT paging-structures 项中的内容来确定的,它们的粒度仅限于用于映射页面的粒度(1 GB、2MB 和 4KB)。

第二段:

粒度可以为 range of 0 and 128B/page。

- 子页面写权限(sub-page write-permission) 允许更精细的粒度控制对 GPA 的写访问。

- 它允许以自然对齐的 128B 子页面粒度控制写访问。也就是说,该功能允许向 4KB 页面所选定的子页面进行写入。

第三段:

将 VM-execution control 的 “sub-page write permissions for EPT” 置 1 来启用子页面写入权限。

第四段:

- Section 28.2.4.1 确定了符合子页面写入权限的访问形式。

- Section 28.2.4.2 解释了处理器如何决定是否允许子页面形式的写访问。

28.2.4.1 Write Access That Are Eligible for Sub-Page Write Permissions

第一段:

子页面写入权限需要 EPT 分页结构项中的位 1 置 0。

- 根据 Section 28.2.3.2,EPT 分页结构项中的位 1 置 0(write access),GPA 禁止写入时,GPA 获得了子页面写入权限。

- 由于其他原因,例如,转换时遇到不存在的 EPT 分页结构项,则不符合子页面写入权限的条件。

第二段:

子页面写入权限需要在 4KB 页面中,并且 EPT PTE 的位 61 为 1。

- GPA 只有在映射到 4KB 页面,并且 EPT PTE 的位 61 (子页面写权限)为 1 时,才有资格获得子页面写权限。

第三段:

5 个不适合子页面访问权限的情况。

对于某些内存访问,处理器会忽略用于映射 4KB 页面的位 61,并且不执行子页面写权限,在这种情况下,满足 Section 28.2.3.2 给出的条件时,该访问导致 EPT Violations。以下访问情况不适合用子页面访问权限:

- 在事务区域(transactional region)内执行的写访问。

- 一个飞地(enclave)对该飞地的 ELRANGE 内的一个地址的写访问。(子页面写权限可能适用于飞地对其 ELRANGE 之外的地址的写访问)

- Intel SGX 指令对飞地页面缓存的访问(enclave page cache)。

- 更新 guest paging-structure 的已访问或脏标志。

- 当访问标志和脏标志被使能,处理器对 guest paging-structure 项的访问。(这种访问会导致 EPT Violations)。

第四段:

不适用于子页面访问权限的例子。

还有一些其它情况,也会导致子页面访问权限不适用,以下列举了一些例子:

- 跨越 4KB 页面的写访问。在这种情况下,除非两页都允许写入,否则任何一页都不能写入。(In this case, sub-page permissions may be applied to neither or to only one of the pages. (There is no write to either page unless the write is allowed to both pages.))

- 由执行多次写访问的指令进行的写访问**(子页写权限主要用于基本指令,如 AND、MOV、OR、TEST、XCHG 和 XOR)**。多次访问内存指令

第五段:

如果 GPA 获得了子页面写入权限,处理器将使用 Section 28.2.4.2 描述的过程来确定是否允许写入该地址。

第六段:

- 如果 GPA 有资格获得子页面写入权限,并且该地址转换为 APIC 访问页面上的地址(Section 29.4),即 “virtualize APIC accessed” VM-excution control wear 0,处理器视作对该地址的写访问。

- 因此,建议软件不要将任何可转换为 APIC 访问页面上的 GPA 赋予有资格获得子页面写入权限。

28.2.4.2 Determining an Access’s Sub-Page Write Permission

第一段:

- 子页面写权限控制对 4KB 页面的 32 个 128B 子页面的每一个单独写访问。

- GPA[11:7] 标识子页面。

第二段:

64 bit SPP 管理一个页面的 32 个子页面的写入权限。

SPP向量:子页号是 S,则如果 2S 处为1,那么允许写入地址。

- 对于每个有资格获得子页面写权限的 GPA,都有一个 64 位的子页面权限向量(SPP)(sub-page permission vector SPP vector)。(64 bit SPP 管理 32 个子页面)

- 4KB 页面上的所有地址都使用相同的 SPP 向量。

- 如果一个地址的子页号(位11:7)是 S,当且仅当子页权限位(SPP) 2S 设置为 1 时,才允许写入地址。(不使用 SPP 向量中奇数位置的位,必须为零)。

第三段:

如何使用 SPP 确定子页面的访问权限?

SPPTP - root SPP table - SPPL3 table - SPPL2 table - SPPL1 table - 查看对应页(GPA[20:12]) 指向偏移,查看该 64 位向量的偏移(子页号 GPA[11:7])

每个页面的 SPP 向量都位于内存中,负责管理符合子页面写入权限的 GPA 的写入,处理器使用以下过程来确定 SPP 向量:

- SPPTP(子页面权限表指针) VM-execution control 包含 4KB 大小的 root SPP table,GPA[47:39] 标识了该表中的一个 64 位项,称为SPPL4E。

- 4KB 的SPPL3 table位于 SPPL4E 所保存的物理地址中。GPA[38:30] 标识了该表中的一个 64 位项,称为 SPPL3E。

- 4KB 的SPPL2 table位于 SPPL3E 所保存的物理地址中。GPA[29:21]标识该表中的一个 64 位项,称为 SPPL2E。

- SPPL2E 保存了 4KB 大小的SPPL1 table的物理地址。GPA[20:12] 标识了该地址的 64 位 SPP 向量。子页许可向量的位 2S 决定了地址是否可以被写入,其中 S 是地址位 11:7 的值。

(用于访问这些表的内存类型在 IA32_VMX_BASIC MSR 的位 53:50 中指出,Appendix A.1)

第四段:

针对写入两个 4KB 页面的情况,分别写入的每个页面?

仅当页面的 SPP 向量中的指示位针对每个子页面时,才允许对单个 4KB 页面上的多个 128B 子页面进行写访问。以下项目适用于访问写入两个 4KB 页面的情况:

- 如果根据 Section 28.2.3.2,不允许对任何一页面进行写入,则即使该页面的 GPA 符合子页面写入权限,也可能不允许访问。(这种情况取决于 model-specific)。

- 只有在以下情况下才允许访问:要么对于每一页,Section 28.2.3.2 允许对该页写入;要么 GPA 有资格获得子页面写许可并且页面的子页面向量允许写入。

第五段:

确定子页面写入权限的 SPP 的分页结构项的存在位 —— SPP miss。

每个项(SPPL4E、SPPL3E、SPPL2E)的位 0 为该项的有效位。如果在映射过程中,发现位 0 为 0,那么映射过程终止,逻辑处理器发生 SPP 未命中(SPP miss)。

第六段:

确定子页面写入权限的 SPP 的分页结构项的保留位置位 —— SPP misconfiguration。

- 每个项(SPPL4E、SPPL3E、SPPL2E)中,保留位 11:1,以及 63:N,其中 N 是处理器的物理地址宽度。如果对保留位置位,则映射过程终止,并且逻辑处理器触发 SPP misconfiguration。

- 奇数位置的 SPP 向量中的位也被保留;SPP misconfiguration 也会发生在当这些向量中的保留位被置位时。

第七段:

SPP-related events(VM exits):SPP miss & SPP misconfiguration

SPP misses 和 SPP misconfigurations 被称为 SPP-related events,二者均会导致 VM exits。

28.2.5 Accessed and Dirty Flags for EPT

第一段:

对于 EPT 中 accessed 和 dirty 的支持查询 MSR IA32_VMX_EPT_VPID_CAP。

- Intel 64 架构支持普通分页结构项(guest)中的accessed和dirty flags。

- 一些处理器还支持 EPT 分页结构项中的相应标志。程序应该读取 VMX 功能 MSR IA32_VMX_EPT_VPID_CAP(Appendix A.10),确定处理器是否支持此功能。

第二段:

accessed 和 dirty flags 的支持由 EPTP 控制。

这两个标志设置后,对 guest 分页结构项的访问被视为写访问。

- 软件可以使用 EPTP 的第 6 位启动 EPT 的 accessed 和 dirty flags,这是一个 VM-execution control field。

- 如果该位为 1,处理器将为 EPT 设置 accessed 和 dirty flags。

- 此外,设置此标志会导致处理器对 guest paging-structure 项的访问被视为写访问。(Section 28.2.3.2)

第三段:

- 对 GPA 的转换使用的所有 EPT paging-structure 项中,第 8 位是 accessed flag。

- 对映射页面的 EPT 分页结构项(与映射另一个 EPT 分页结构相反),第 9 位是 dirty flags。

第四段:

每当处理器使用 EPT 分页结构项进行 GPA 转换时,它就在该项中设置 accessed flag。

- 每当处理器使用 EPT 分页结构项进行 GPA 转换时,它就在该项(EPT 硬件)中设置 accessed flag。

第五段:

每当对 GPA 进行写入时,处理器在 EPT 分页结构项中设置 dirty flag

- 每当对 GPA 进行写入时,处理器在 EPT 分页结构项中(EPT 硬件)设置 dirty flag。

- 该项在标识 GPA 的最终物理地址(EPT PTE 或 EPT 分页结构项,其中位 7 为 1,PS?),(由于该项映射了页面)

第六段:

同前文。

- 当 EPT 的 accessed 和 dirty flags 启用时,处理器对 guest 分页结构项的访问被视为写入(Section 28.2.3.2)。

- 因此,这样的访问将导致处理器在 EPT paging-structure 项中设置 dirty flags,该 dirty flags 标识了指向最终物理地址的 guest paging-structure 项。

第七段:

那些加载的 guest PDPTEs 被视为读取,不会导致处理器在任何 EPT 分页结构项中设置 dirty flags。

- 这不适用于通过 MOV to CR 指令为 PAE 分页加载 PDPTE 寄存器,参见 Section 4.4.1,那些加载的 guest PDPTEs 被视为读取,不会导致处理器在任何 EPT 分页结构项中设置 dirty flags。(没有实际访问物理内存)

第八段:

- 这些标志是“粘性的”,意味着一旦设置,处理器就不会清除它们,只有程序可以清除它们。

第九段:

缓存相关情况中,accessed 和 dirty flags 并不会被处理器及时恢复。

- 处理器可以在 TLBs 和分页结构缓存中(Section 28.3) 缓存来自 EPT paging-structure 的项。

- 这一事实意味着,如果软件将 accessed 或者 dirty flags 从 1 置为 0,处理器可能不会在后续访问中将受影响的 GPA 相关的分页结构项置位。

28.2.6 Page-Modification Logging

第一段:

page-modification log(页面修改日志记录):跟踪对 GPA 的写入。

- 当 accessed 和 dirty flags 启用时,软件可以使用称为页面修改日志记录(page-modification logging)的功能来跟踪对 GPA 的写入。

第二段:

处理器将 GPA 添加到 page-modification log。

page-modification log 由 512 个 8B 项组成,位于 PML address VM-execution control field,由位于 VM-execution control field 的 PML 索引指向需要使用的项。

- 软件可以通过设置“enable PML” VM-excution control(Table 24-7 Section 24.6.2) 来启用 page-modification logging。

- 当该位为 1 时,处理器将 GPA 添加到 page-modification log。

- page-modification log 是一个 4KB 的内存区域,物理地址位于 PML address VM-execution control field。

- page-modification log 由 512 个 64 位项组成;PML 索引 VM-execution control field 指示下一个要使用的项。

第三段:

在 GPA 转换之前,处理器可能会将 accessed 和 dirty flags 置位。

在 GPA 转换之前,处理器会检查 PML 索引是否在 0-511,如果不在,出现 page-modification log-full event 错误,同时 VM exit,也不会继续将 GPA 转换。

- 在允许 GPA 访问之前,处理器可能会为 EPT 将 accessed 和 dirty flags 置位(Section 28.2.5)。

- 在 GPA 访问之前,处理器检查 PML 索引。如果 PML 索引不在 0-511 的范围内,则会出现 page-modification log-full event,并出现 VM exit,在这种情况下,不会将 accessed 和 dirty flags 置位,也不会触发事件的 GPA 访问。

第四段:

如果处理器将 EPT 的 accessed 或 dirty flags 从 0 变为 1:GPA 被写入 page-modification log。2. PML 索引减一。

检查是否在 0-511。

- 相反,如果 PML 索引在 0-511 的范围内,处理器将按照 Section 28.2.5 所述的,更新 EPT 的 accessed 或 dirty flags。

- 如果处理器更新了 EPT 的 accessed 和 dirty flags(从 0 更改为 1),则它的操作如下:

- GPA 的访问被写入 page-modification log。具体来说,GPA 被写入到偏移量为 PML 索引值的 8 倍的 PML 地址处。写入值的位 11:0 始终为 0。

- PML 索引递减 1(这可能导致该值从 0 转变为 FFFFH)。

- 因为处理器随着每个日志项递减 PML 索引,所以该值可能从 0 转变为 FFFFH(16位字段?)。此时不会发生进一步的日志记录,因为处理器将确定 PML 索引不在 0-511 范围内,并将生成 page-modification log-full event。

28.2.7 EPT and Memory Typing

- 本节说明了在使用 EPT 时,逻辑处理器如何确定用于内存访问的内存类型。(详见 “Memory Cache Control” of Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A for details of memory typing in the Intel 64 architecture.)

- Section 28.2.7.1 解释了如何访问 EPT 分页结构项来确定内存类型。

- Section 28.2.7.2 解释了如何使用 EPT 转换的 GPA 来确定访问的内存类型。

28.2.7.1 Memory Type Used for Accessing EPT Paging Structures

CR0.CD=0,EPT 分页结构项根据 EPTP[2:0] 确定访问的内存类型。否则,均为 UC。

CR0.PG=0,EPT ON 时?

本节说明如何访问 EPT 分页结构来确定内存类型,基于控制器寄存器 CR0 中的位 30(高速缓冲禁用——CD)的值:

- 如果 CR0.CD=0,用于此类引用的内存类型是 EPT paging-structure 内存类型,它被 EPTP 的位 2:0 指定,是一个VM-execution control field(Section 24.6.11)。值 0 表示不可缓存类型(UC),值 6 表示回写类型(WB),其它值保留。

- 如果 CR0.CD=1,内存类型均指 UC。

MTRRs 对用于访问 EPT 分页结构的内存类型没有影响。

27.2.7.2 Memory Type Used for Translated Guest-Physical Addresses

- 在使用 guest paging-structure 转换 GPA 时,内存类型由 PAT(页面属性表) 决定:

CR0.PG=0:PAT 内存类型为 WB

CR0.PG=1:PAT 内存类型却决于 IA32_PAT MSR “Selecting a Memory Type from the PAT”。 - 在使用 EPT 进行转换时,内存类型由 EPT 的最后一个分页结构项中的 5:3 指定 0=UC;1=WC;4=WT;5=WP;6=WB:

CR0.CD=0,有效内存类型取决于最后一个 EPT 分页结构项的第 6 位的值:如果该值为 0,则有效内存类型为 EPT 内存类型和 PAT 内存类型的组合;如果该值为1,则用于访问的内存类型为 EPT 内存类型,PAT 内存类型被忽略。

CR0.CD=1,有效内存类型为 UC。

使用 GPA(使用 EPT 转换)的内存访问的有效内存类型是用于访问内存的内存类型。有效内存类型基于控制寄存器 CR0 中的位 30(缓存禁用——CD)的值;用于转换 GPA 的最后一个分页结构项(EPT PDE[7]=1,EPT PTE[7]=1);PAT(页面属性表)存储类型:

- PAT 存储类型取决于 CR0.PG:

- CR0.PG=0,PAT 内存类型为 WB;

- CR0.PG=1,PAT 内存类型取决于 IA32_PAT MSR “Selecting a Memory Type from the PAT”。

- EPT 内存类型在最后一个 EPT 分页结构项的位 5:3 中指定 0=UC;1=WC;4=WT;5=WP;6=WB。其它值被保留并导致 EPT misconfigurations(Section 28.2.3)。

- CR0.CD=0,有效内存类型取决于最后一个 EPT 分页结构项的第 6 位的值:

- 如果该值为 0,则有效内存类型为 EPT 内存类型和 PAT 内存类型的组合,Table 11-7,Section 11.5.2.2,使用 EPT 内存类型代替 MTRR 内存类型。

- 如果该值为1,则用于访问的内存类型为 EPT 内存类型,PAT 内存类型被忽略。

- 如果 CR0.CD=1,有效内存类型为 UC。

MTRRs 对用于访问 GPA 的内存类型没有影响。

28.3 CACHING TRANSLATION INFORMATION

第一段:

本节介绍了与 VMX 相关的缓存。

- 通过在处理器上缓存来自转换过程中的数据来加速地址转换过程。

- In Section 4.10, “Caching Translation Information” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A.当前部分描述了该缓存如何与 VMX 交互。

第二段:

- VMX 操作的 VPID 和 EPT 功能完善了这种缓存体系结构。

- EPT 定义了 GPA 空间,并定义了到该地址空间(从线性地址空间)和从该地址空间(到物理地址空间)的转换。这两个特性控制逻辑处理器创建和使用从分页结构缓存的信息的方式。

第三段:

- Section 28.3.1。描述了可以缓存的不同类型的信息。

- Section 28.3.2。规定了何时可以缓存此类信息以及如何使用。

- Section 28.3.3。说明了软件如何使缓存信息无效。

28.3.1 Information That May Be Cached

第一段:

两种缓存内容:线性页号到物理页号的映射;线性页码转换时的分页结构项;

- Section 4.10, “Caching Translation Information” in Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A 确定了逻辑处理器可以缓存的两种转换相关信息:

- translations,从线性页码到物理页面帧的映射;

- paging-structure caches,线性页码的高位映射到来自分页结构项的信息,用于转换与这些高位匹配的线性地址。

第二段:

3 种缓存形式。

当使用 VPIDs 和 EPT 时,可以缓存相同种类的信息。逻辑处理器可以基于其功能来缓存和使用这样的信息,具有不同功能的信息标识如下:

- Linear mappings。有两种类型:

(GVA-HPA?)线性页号到物理页号的映射,一步到位;对于分页结构缓存,对应线性地址高端到物理地址高端的分页结构缓存的映射。

不会使用 EPT。

- 线性地址转换。其中每一个都是从线性页码到它所转换的物理页面帧的映射,以及关于关于访问权限和内存类型的信息。

- 线性分页结构缓存项。每一个都是从线性地址的高端到用于转换线性地址空间的相应区域的分页结构的物理地址的映射,以及关于访问权限的信息。例如,线性地址的第 47:39 位将映射到相关页面 PDPT 的地址。

线性映射不包含来自任何 EPT 分页结构的信息。

- Guest-physical mappings。有两种类型:

GPA-HPA,可以不使用 guest-paging structures,需要使用 EPT 继续映射地址。

- Guest-physical 转换。每一个都从 guest-physical 页号到物理页帧的映射,以及关于访问权限和内存类型的信息。

- Guest-physical 的分页结构缓存项。每一个都是从 GPA 的上部到 EPT 分页结构的物理地址的映射,用于转换客户物理地址空间的相应区域,以及关于访问权限的信息。

guest-physical mappings 中包含来自 EPT 分页结构项的关于访问权限和内存类型的信息。

- Combined mappings。包含两个方面:

(GVA-HPA?)会使用到 guest paging structures 和 EPT。

- 组合转换。其中每一个都是从线性页码到它所转换的物理页帧的映射,以及关于访问权限和内存类型的信息。

- 组合分页结构缓存项。每一个都是从线性地址的高端到用于转换线性地址空间的相应区域的分页结构的物理地址的映射,以及关于访问权限的信息。

关于访问权限和内存类型的组合映射中的信息是从 guest paging structures 和 EPT 分页结构中得到的。

Guest-physical mappings 和 Combined mappings 也可能包括 SPP 向量和用于定位 SPP 向量的数据结构信息。(Section 28.2.4.2)

Linear mappings 和 Combined mappings 二者区别?

- 前者不包含来自分页结构的信息,后者包含 guest 中的分页结构项信息和 EPT 分页结构项中的信息。

Guest-physical mappings 和 Combined mappings 二者区别?

- 前者的 EPT 来源于 EPTP 所指向的 EPT 分页结构项;后者则来自于 EP4TA 所指向的 EPT 分页结构项。

28.3.2 Creating and Using Cached Translation Information

以下内容详细介绍三种映射的创建:

- 以下内容描述了在不使用 EPT 时映射的创建(包括 outside VMX non-root operation 的执行):

- 创建Linear mappings。它们来自当前值 CR3 引用的分页结构(直接或间接),并且与当前 VPID 和当前 PCID 相关联。

- 不使用从不存在或将保留位置位了的分页结构项中的信息来创建Linear mappings。例如,如果 PTE 不存在,则不会为其映射所使用的该 PTE 的任何线性页码创建Linear mappings。

- EPT 不使用时,不会创建Guest-physical mappings或Combined mappings。

- 以下内容描述了使用 EPT 时映射的创建:

- Guest-physical mappings被创建。它们源自当前 EPTP 的位 51:12 所引用的 EPT 分页结构(直接或间接)。这 40 位包含 EPT-PML4 table 的地址。(符号 EP4TA 指的是那 40 位)。新创建的Guest-physical mappings与当前 EP4TA 相关联。

- 可以创建Combined mappings。它们源自当前 EP4TA 引用的 EPT 分页结构(直接或间接)。如果 CR0.PG=1,它们是从 CR3 的当前值映射的分页结构(直接或间接)中产生的。它们与当前的 VPID、当前的 PCID 和当前的 EP4TA 相关联。如果 CR0.PG=0,则不会创建组合分页结构缓存项。

- 不使用从不存在(Section 28.2.2)或配置错误(Section 28.2.3.1)的EPT分页结构项中派生的信息创建Guest-physical mappings或Combined mappings。

- 不使用从不存在或设置保留位的 guest paging-structure 项中导出的信息来创建Combined mappings。

- 在使用 EPT 时,不会创建Linear mappings。

以下内容详细介绍了各种映射的使用:

- 如果不使用 EPT,逻辑处理器可以使用如下的缓存映射:

不使用 EPT,逻辑处理器可以使用:

- Linear mappings(与当前 VPID 和当前 PCID 相关联)

- 全局 TLB(与当前 VPID 和任何 PCID 相关联)

- 对于使用线性地址的访问,它可以使用与当前 VPID 和当前 PCID 相关联的Linear mappings。它还可以使用与当前 VPID 和任何 PCID 相关联的全局 TLB 项(Linear mappings)。

- EPT 不使用时,不使用Guest-physical mappings或Combined mappings。

- 如果正在使用 EPT,逻辑处理器可以使用缓存映射,如下所示:

使用 EPT,逻辑处理器可以使用:

- Combined mappings(当前 VPID、当前 PCID、当前 EP4TA 相关联)

- 全局 TLB(当前 VPID、当前 EP4TA 和任何 PCID 相关联)

- 对于使用线性地址的访问,它可以使用与当前 VPID、当前的 PCID 和当前 EP4TA 相关联的Combined mappings。它还可以使用与当前 VPID、当前 EP4TA 和任何 PCID 相关联的全局 TLB 项(Combined mappings)。

- 对于使用 GPA 的访问,它可以使用与当前 EP4TA 相关联的 guest-physical 映射。

- 在使用 EPT 时,不使用Linear mappings。

28.3.3 Invalidating Cached Translation Information

- 软件对于分页结构(包括 EPT 分页结构)的修改可能会导致这些结构与逻辑处理器缓存的映射之间不一致。

- 某些操作会使逻辑处理器缓存的信息无效,并可用于消除这种不一致。

28.3.3.1 Operations that Invalidate Cached Mappings

以下操作会导致缓存无效:

- 独立于 VMX 操作在体系结构上使 TLB 或分页结构高速缓冲中的项无效的操作(例如,INVLPG和INVPCID)使Linear mappings和Combined mappings无效。这些操作只为当前的 VPID(对于Combined mappings,所有的 EP4TAs)这样做。即使使用了 EPT,当前 VPID 的线性映射也会失效;即使未使用 EPT,当前 VPID 的组合映射也会失效。

- EPT violation会使任何用于转换 GPA 的Guest-physical mappings无效(与当前 EP4TA相关联)。如果该 GPA 是线性地址的转换,则EPT violation还会使与当前 PCID、VPID 和 EP4TA 相关联的该线性地址的任何Combined mappings无效。

- 如果 “enable VPID” VM-execution control 为 0,VM entries 和 VM exits 将使与 VPID 0000H 相关联的Linear mappings和Combined mappings无效(对于所有 PCIDs),VPID 0000H 的Combined mappings对所有 EP4TAs 无效。

- INVVPID指令的执行使Linear mappings和Combined mappings无效。该指令基于传递的操作数,称为 INVVPID 类型和 INVVPID 描述符。目前定义了四种 INVVPID类型:

- Individual-address。如果 INVVPID 类型为 0,则逻辑处理器与 INVVPID 描述符中指定的 VPID 相关联的Linear mappings和Combined mappings,并且该Linear mappings和Combined mappings将用于转换 INVVPID 描述符中指定的线性地址。该 VPID 和线性地址的Linear mappings和Combined mappings对所有 PCIDs 无效,对于Combined mappings,对所有 EP4TAs 无效。

- Single-context。如果 INVVPID 类型为 1,则逻辑处理器使与 INVVPID 描述符中指定的 VPID 相关联的所有Linear mappings和Combined mappings无效。该 VPID 的Linear mappings和Combined mappings对所有 PCIDs 无效,对于Combined mappings,对所有 EP4TAs 无效。

- All-context。如果 INVVPID 类型为 2,则逻辑处理器会使与除 VPID 0000H 之外的所有 VPID 和所有 PCIDs 相关联的Linear mappings和Combined mappings无效。(该指令也可能使 VPID 0000H 的Linear mappings无效)Combined mappings对所有 EP4TAs 无效。

- Single-context-retaining-globals。如果 INVVPID 类型为 3,则逻辑处理器使与 INVVPID 描述符中指定的 VPID 相关联的Linear mappings和Combined mappings无效。该 VPID 的Linear mappings和Combined mappings对所有 PCIDs 无效,对于Combined mappings,对所有 EP4TAs 无效。逻辑处理器不需要将全局转换的信息无效,Section 4.10,“Caching Translation Information” (该指令还能可能使与其它 VPIDs 相关联的映射无效)

- INVEPT指令的执行使得Guest-physical mappings和Combined mappings无效。无效基于指令操作数,称为 INVEPT 类型和 INVEPT 描述符。目前定义了两种 INVEPT 类型:

- Single-context。如果 INVEPT 类型为 1,则逻辑处理器使与 INVEPT 描述符中指定的 EP4TA 相关联的所有Guest-physical mappings和Combined mappings无效。该 EP4TA 的Combined mappings对所有 VPIDs 和所有的 PCIDs 无效。(该指令可能会使与其它 EP4TAs 相关联的映射无效)

- All-context。如果 INVEPT 类型为 2,则逻辑处理器使与所有 EP4TAs 相关联的Guest-physical mappings和Combined mappings无效(对于Combined mappings,对于所有的 VPIDs 和 PCIDs)。

关于 INVEPT 说明的详细信息,参考 Chapter 30。

- 通电或重置会使所有Linear mappings、Guest-physical mappings和Combined mappings无效。

28.3.3.2 Operations that Need Not Invalidate Cached Mappings

以下内容详细说明了不会使某些缓存映射无效的操作情况:

- 独立于 VMX 操作在体系结构上使 TLB 或分页结构缓存中的条目无效的操作不需要使任何Guest-physical mappings无效。

- INVVPID 指令不需要使任何Guest-physical mappings无效。

- INVEPT 指令不需要使任何Linear mappings无效。

- VMX transitions 不需要使任何Guest-physical mappings无效。如果 “enable VPID” VM-execution control 为 1,则不需要 VMX transitions 来使任何Linear mappings或Combined mappings无效。

- VMXOFF 和 VMXON 指令不需要使任何Linear mappings、Guest-physical mappings或Combined mappings无效。

逻辑处理器可以随时使任何缓存的映射无效。由于这个原因,上面识别的操作可能使指示的映射无效,尽管不需要这样做。

28.3.3.3 Guidelines for Use of the INVVPID Instruction

第一段:

VMM 软件使用 INVVPID 指令的需求取决于该软件如何虚拟化内存(Section 32.3 Memory Virtualization)。

第二段:

- 如果未使用EPT,VMM很可能正在虚拟化 guest paging-structure。这样的VMM可以配置VMCS,使得使TLB和分页结构高速缓存的条目无效的所有或一些操作(例如,INVLPG指令)导致虚拟机退出。如果VMM软件正在模拟这些操作,可能有必要使用INVVPID指令来确保逻辑处理器的TLB和分页结构缓存被适当地无效。

第三段:

软件何时应该使用INVVPID指令的要求取决于用于页表虚拟化的特定算法。以下项目为软件开发人员提供了指南:

- INVLPG指令的仿真可能需要执行INVVPID指令,如下所示:

- INVVPID类型是个人地址(0)。

- INVVPID描述符中的VPID是分配给被仿真执行的虚拟处理器的。

- INVVPID描述符中的线性地址是被仿真的INVLPG指令的操作数。

- 有些指令会使顶级域名和分页结构缓存中的所有条目无效——除了全局翻译。一个例子是MOV到CR3指令。(有关全球翻译的详细信息,请参见第3A卷《英特尔64和IA-32架构软件开发人员手册》中的第4.10节“缓存翻译信息”。)这种指令的仿真可能需要执行如下的INVVPID指令:

- INVVPID类型是单上下文保留全局(3)。

- INVVPID描述符中的VPID是分配给被仿真执行的虚拟处理器的。

- 有些指令会使TLB和分页结构缓存中的所有条目无效,包括全局翻译。例如,如果第4位(页面全局使能—PGE)的值发生变化,则执行MOV至CR4指令。这种指令的仿真可能需要执行如下的INVVPID指令:

- INVVPID类型是单上下文(1)。

- INVVPID描述符中的VPID是分配给被仿真执行的虚拟处理器的。

第四段:

- 如果未使用EPT,逻辑处理器会将其创建的所有映射与当前VPID相关联,并使用这些映射来转换线性地址。因此,VMM不应该对使用不同页面表的不同非EPT客人使用相同的VPID。这样做可能会导致一位客人使用与另一位客人相关的翻译。

第五段:

- 如果正在使用EPT,上面列举的指令可能不会被配置为导致虚拟机退出,并且VMM可能不会模仿它们。在这种情况下,客户软件对指令的执行会使顶级域名和分页结构缓存中所需的条目失效(参见第28.3.3.1节);不需要执行INVVPID指令。

第六段:

- 如果正在使用EPT,逻辑处理器会将其创建的所有映射与当前EPTP的位51:12的值相关联。如果一个VMM对不同的客人使用不同的EPTP价值观,它可能会对这些客人使用相同的VPID。这样做不会导致一个客人使用属于另一个客人的翻译。

第七段:

以下指南适用范围更广,即使正在使用EPT也是合适的:

- 如第29.4.5节所述,如果软件没有正确地使可能从分页结构中缓存的信息无效,对APIC访问页的访问可能不会导致APIC访问虚拟机退出。如果在某个时间,逻辑处理器上的当前VPID是非零值X,则建议软件在建立VPID X的同一逻辑处理器上的虚拟机条目之前,使用“单上下文”INVVPID类型的INVVPID指令和INVVPID描述符中的VPID X,并且(a)“虚拟APIC访问”虚拟机执行控制从0更改为1;或者(b)APIC接入地址的值被改变。

- 软件可以在执行VMXON指令之后或执行VMXOFF指令之前立即使用“全上下文”INVVPID类型的INVVPID指令。这两种方法都可以防止在VMX操作的不同使用之间,对从分页结构中缓存的信息进行潜在的不希望有的保留。

28.3.3.4 Guidelines for Use of the INVEPT Instruction

以下项目提供了使用INVEPT指令使从EPT分页结构缓存的信息无效的指南。

- 在对EPT分页结构条目进行以下任何更改后,软件应使用“单上下文”INVEPT类型的INVEPT指令(INVEPT描述符应包含直接或间接引用修改后的EPT分页结构的EPTP值):

- 将任何特权位2:0从1更改为0。

- 更改位51:12中的物理地址。

- 如果被访问,清除位8(被访问标志),EPT的脏标志将被启用。

- 对于EPT PDPTE或EPT PDE,更改位7(决定条目是否映射页面)。

- 最后一个EPT分页结构条目,用于转换客户物理地址(位7设置为1的EPT PDPTE、位7设置为1的EPT PDE或EPT PTE),更改位5:3或位6。(这些位决定了使用EPT分页结构条目的有效内存访问类型;参见第28.2.7节。)

- 最后一个用于转换客户物理地址的EPT分页结构条目(位7设为1的EPT PDPTE、位7设为1的EPT PDE或EPT PTE),如果被访问,清除位9(脏标志),EPT的脏标志将被启用。

- 软件应在EPTP值为X的虚拟机条目之前使用具有“单上下文”INVEPT类型的INVEPT指令,以便如果逻辑处理器先前在EPTP值为Y的VMX非根操作中,则X[6]= 1(EPT的访问和脏标志被启用),并且Y[51:12] = X[51:12]。

- 软件可以在修改现有的EPT分页结构条目(见第28.2.2节)后使用INVEPT指令,将任何特权位2:0从0更改为1。如果不这样做,可能会导致违反EPT,否则不会发生。因为EPT违规会使导致EPT违规的访问所使用的任何映射无效(参见第28.3.3.1节),所以如果再次执行原始访问,即使不执行INVEPT指令,EPT违规也不会再次发生。

- 因为逻辑处理器不会缓存从不存在(参见第28.2.2节)或配置错误(参见第28.2.3.1节)的EPT分页结构条目中获得的任何信息,所以在对不存在或配置错误的EPT分页结构条目进行修改后,没有必要执行INVEPT。

- 如第29.4.5节所述,如果软件没有正确地使从EPT分页结构中缓存的信息无效,对APIC访问页的访问可能不会导致APIC访问虚拟机退出。如果EPT曾在逻辑处理器上与EPTP X一起使用,建议软件在同一逻辑处理器上启用EPT与EPTP X以及(a)“虚拟化APIC访问”虚拟机执行控制从0更改为1之前,在INVEPT描述符中使用“单上下文”INVEPT类型和EPTP X的INVEPT指令;或者(b)APIC接入地址的值被改变。

- 软件可以在VMXON指令执行之后或VMXOFF指令执行之前立即使用“全上下文”INVEPT类型的INVEPT指令。这两种方法都可以防止在VMX操作的不同使用之间,从EPT分页结构中缓存的信息被潜在的不希望有的保留。

在包含一个以上逻辑处理器的系统中,软件必须考虑这样一个事实,即来自EPT分页结构条目的信息可能被缓存在修改该条目的逻辑处理器之外的逻辑处理器上。将更改传播到分页结构条目的过程通常被称为“TLB击落”《英特尔64和IA-32架构软件开发人员手册》第3A卷第4.10.5节“分页结构变化向多处理器的传播”对TLB击落进行了讨论。