目录

🍓基本地址变换机构

🍒对页表项大小的进一步探讨

🥭具有快表的地址变换机构

🌽 什么是快表(TLB)

🥕引入快表后,地址的变换过程

🥒局部性原理

🍉两级页表

🧅单级页表存在的问题

🍍如何解决单级页表的问题?

问题一:

🍅1. 两级页表的原理、地址结构

🥝 2. 如何实现地址变换

问题二:

🍆 1. 需要注意的几个细节

🍪基本分段存储管理方式

🥥 分段

🍦段表

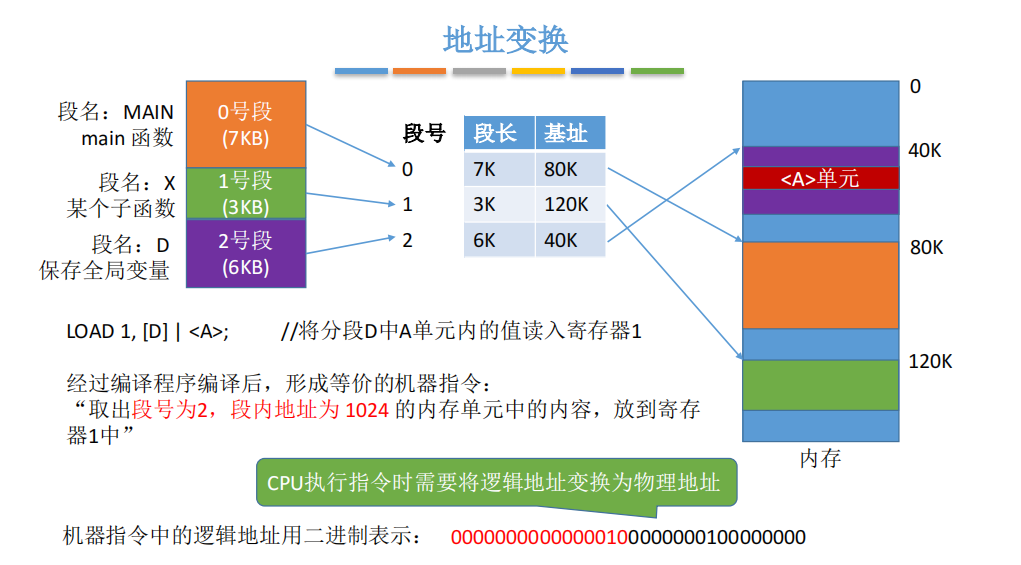

🧊地址变换

🍋 分段、分页管理的对比

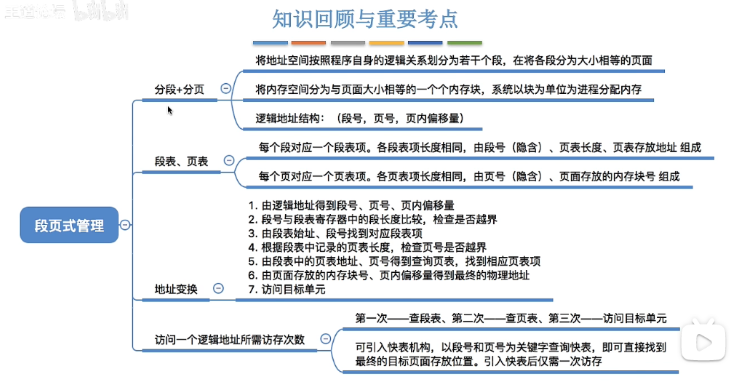

🍎段页式管理方式

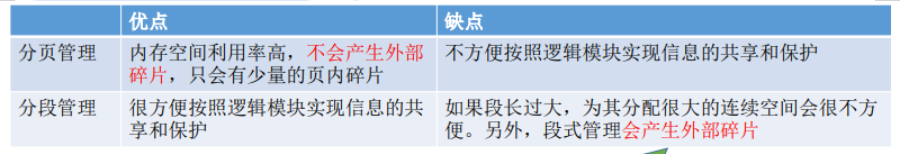

🧀 分页、分段的优缺点分析

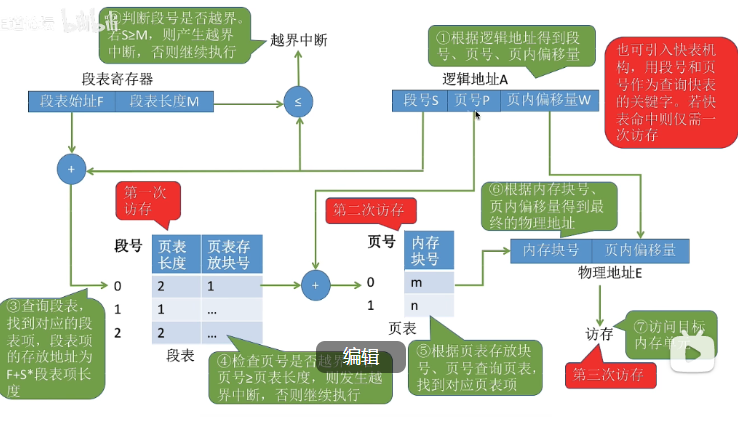

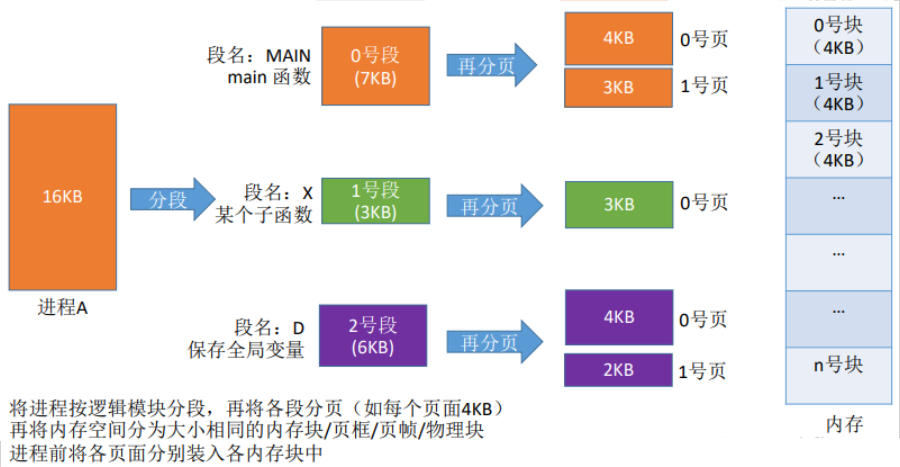

🧇 分段+分页=段页式管理

🌮段页式管理的逻辑地址结构

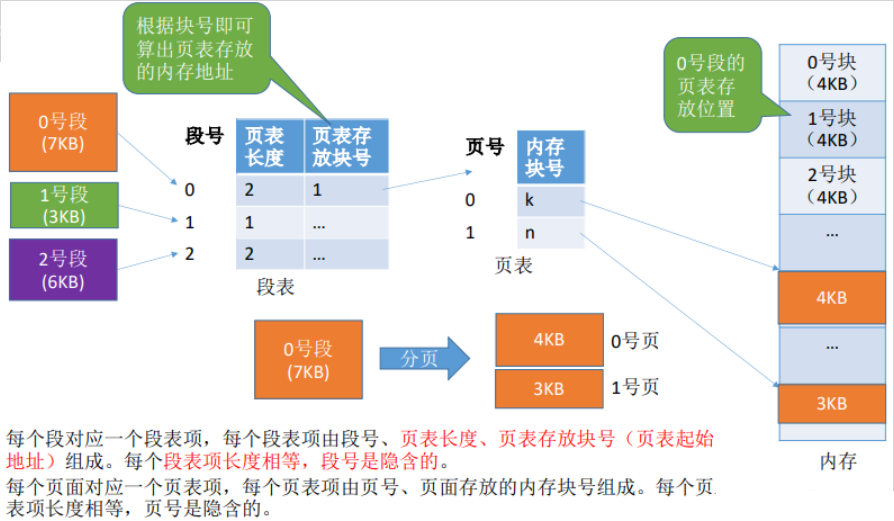

🍞段表、页表

🌎个人主页:个人主页 ☀️系列专栏:操作系统

🍓基本地址变换机构

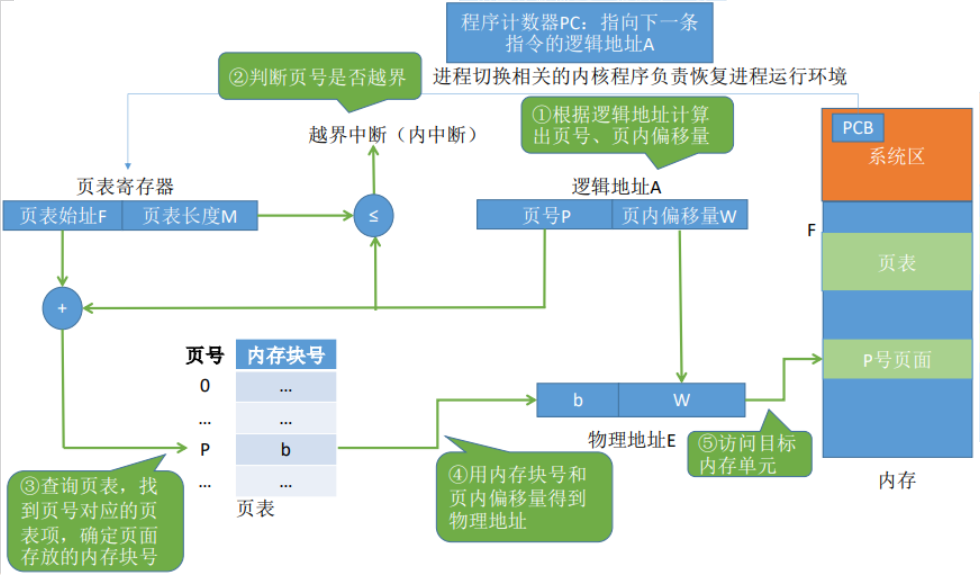

- 结合上一小节理解基本地址变换机构(用于实现逻辑地址到物理地址转换的一组硬件机构)的原理和流程

- 基本地址变换机构可以借助进程的页表将逻辑地址转换为物理地址。

- 通常会在系统中设置一个页表寄存器(PTR),存放页表在内存中的起始地址F和页表长度M。

- 进程未执行时,页表的始址 和 页表长度放在进程控制块(PCB)中,当进程被调度时,操作系统内核会把它们放到页表寄存器中。

- 注意:页面大小是2的整数幂

- 设页面大小为L,逻辑地址A到物理地址E的变换过程如下:

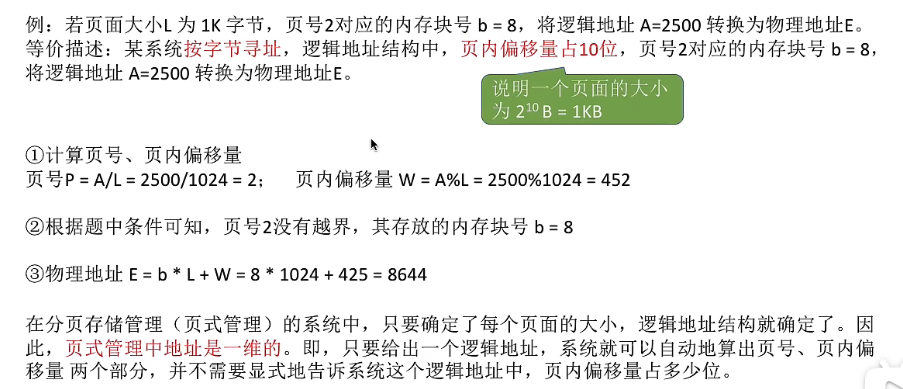

- ①计算页号 P 和页内偏移量W( 如果用十进制数手算,则 P=A/L,W=A%L;但是在计算机实际运行时,逻辑地址结构是固定不变的,因此计算机硬件可以更快地得到二进制表示的页号、页内偏移量)

- ②比较页号P 和页表长度M,若 P≥M,则产生越界中断,否则继续执行。(注意:页号是从0开始的,而页表长度至少是1,因此 P=M 时也会越界)

- ③页表中页号P对应的页表项地址 = 页表起始地址F + 页号P * 页表项长度,取出该页表项内容b,即为内存块号。(注意区分页表项长度、页表长度、页面大小的区别。页表长度指的是这个页表中总共有几个页表项,即总共有几个页;页表项长度指的是每个页表项占多大的存储空间;页面大小指的是一个页面占多大的存储空间)

- ④计算E = b * L + W,用得到的物理地址E 去访存。(如果内存块号、页面偏移量是用二进制表示的,那么把二者拼接起来就是最终的物理地址了)

- 动手验证:假设页面大小 L = 1KB,最终要访问的内存块号b = 2,页内偏移量W= 1023。

①尝试用 E = b * L + W 计算目标物理地址。

②尝试把内存块号、页内偏移量用二进制表示,并把它们拼接起来得到物理地址。

对比①、②的结果是否一致。

🍒对页表项大小的进一步探讨

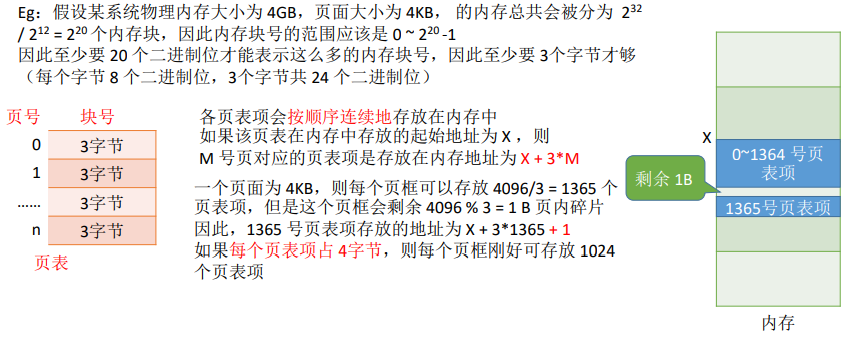

每个页表项的长度是相同的,页号是“隐含”的

- 结论:理论上,页表项长度为 3B 即可表示内存块号的范围,但是,为了方便页表的查询,常常会让一个页表项占更多的字节,使得每个页面恰好可以装得下整数个页表项。

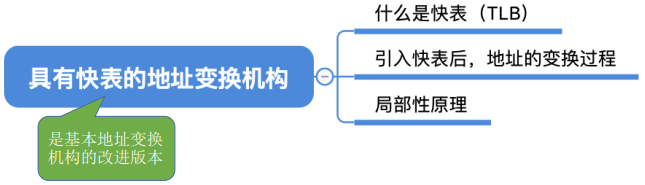

🥭具有快表的地址变换机构

🌽 什么是快表(TLB)

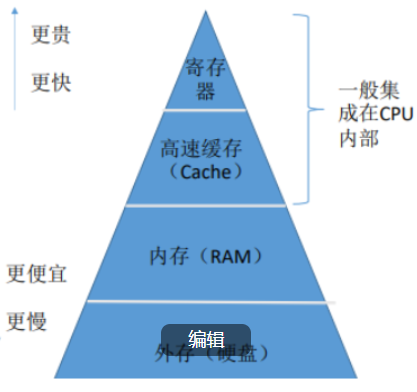

- 快表,又称联想寄存器(TLB, translation lookaside buffer ),是一种访问速度比内存快很多的高速缓存( TLB不是内存! ),用来存放最近访问的页表项的副本,可以加速地址变换的速度。

- 与此对应,内存中的页表常称为慢表。

🥕引入快表后,地址的变换过程

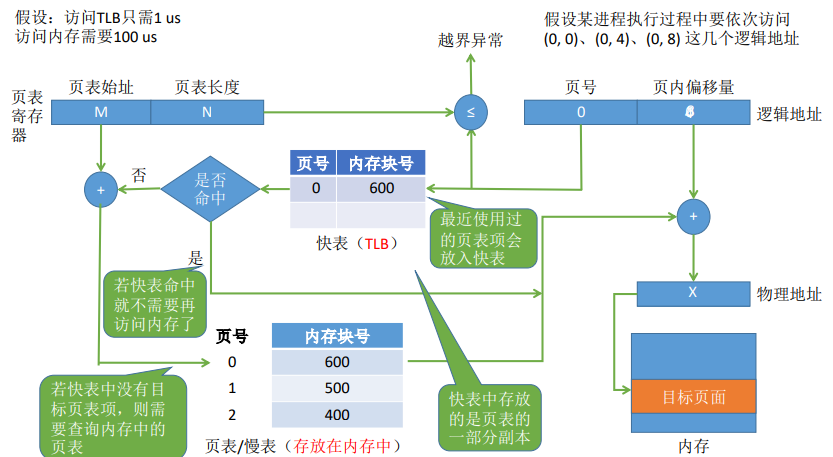

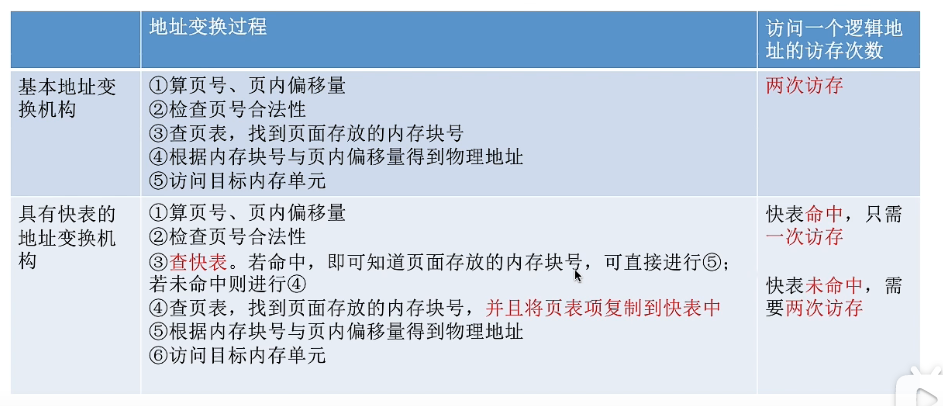

① CPU给出逻辑地址,由某个硬件算得页号、页内偏移量,将页号与快表中的所有页号进行比较。

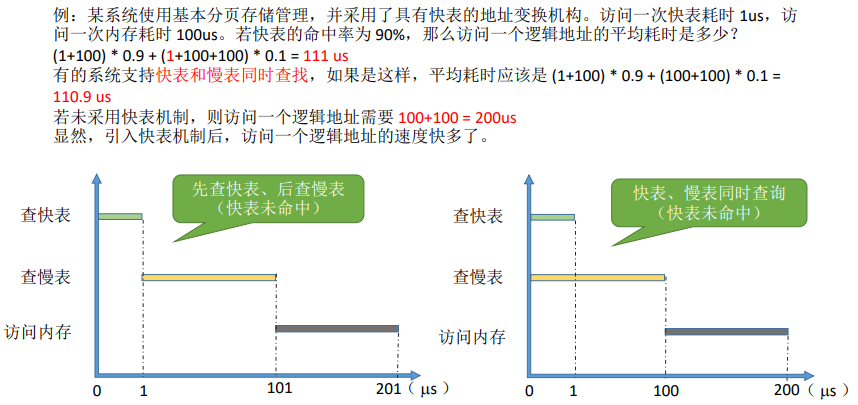

② 如果找到匹配的页号,说明要访问的页表项在快表中有副本,则直接从中取出该页对应的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表命中,则访问某个逻辑地址仅需一次访存即可。

③ 如果没有找到匹配的页号,则需要访问内存中的页表,找到对应页表项,得到页面存放的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表未命中,则访问某个逻辑地址需要两次访存(注意:在找到页表项后,应同时将其存入快表,以便后面可能的再次访问。但若快表已满,则必须按照一定的算法对旧的页表项进行替换)

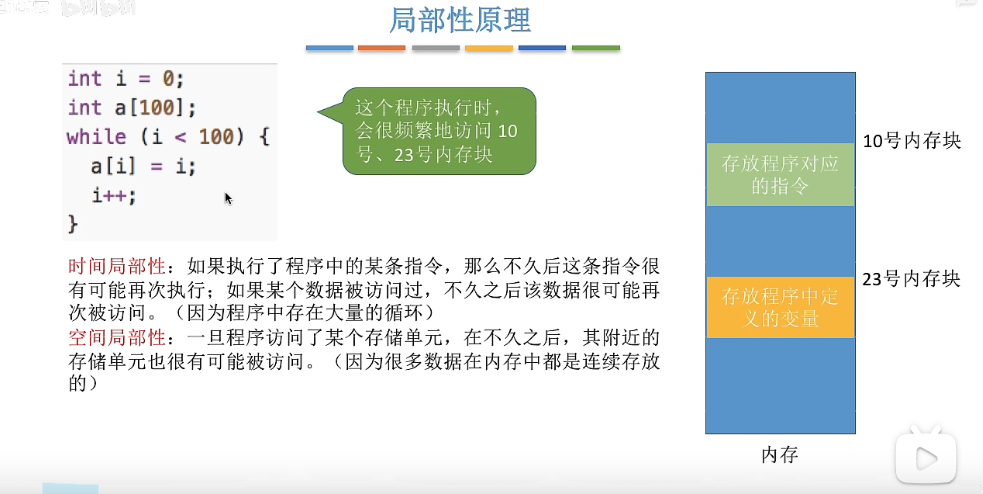

由于查询快表的速度比查询页表的速度快很多,因此只要快表命中,就可以节省很多时间。因为局部性原理,一般来说快表的命中率可以达到 90% 以上。

🥒局部性原理

🍉两级页表

🧅单级页表存在的问题

- 根据局部性原理可知,很多时候,进程在一段时间内只需要访问某几个页面就可以正常运行了。因此没有必要让整个页表都常驻内存。

🍍如何解决单级页表的问题?

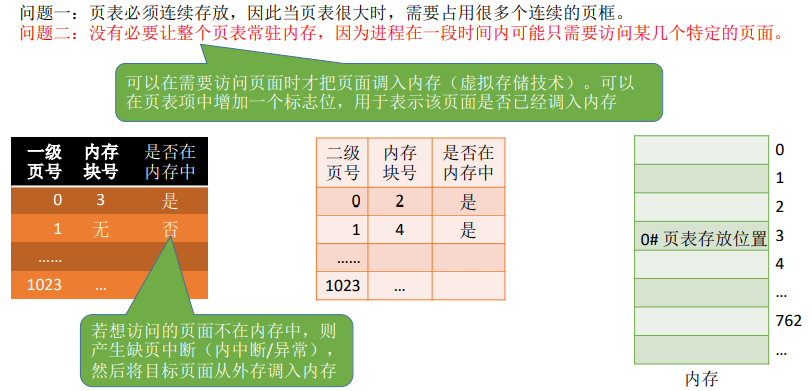

问题一:

页表必须连续存放,因此当页表很大时,需要占用很多个连续的页框。

- 把页表再分页并离散存储,然后再建立一张页表记录页表各个部分的存放位置,称为 页目录表,或称 外层页表,或称 顶层页表

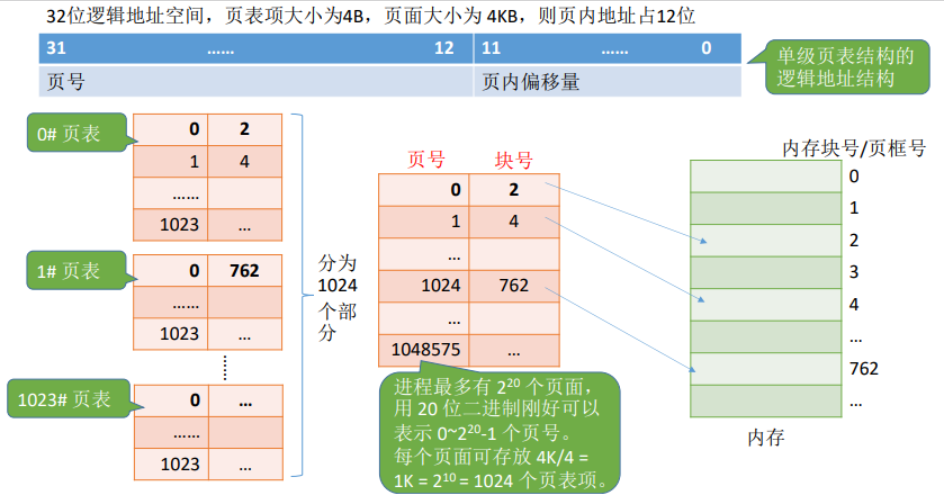

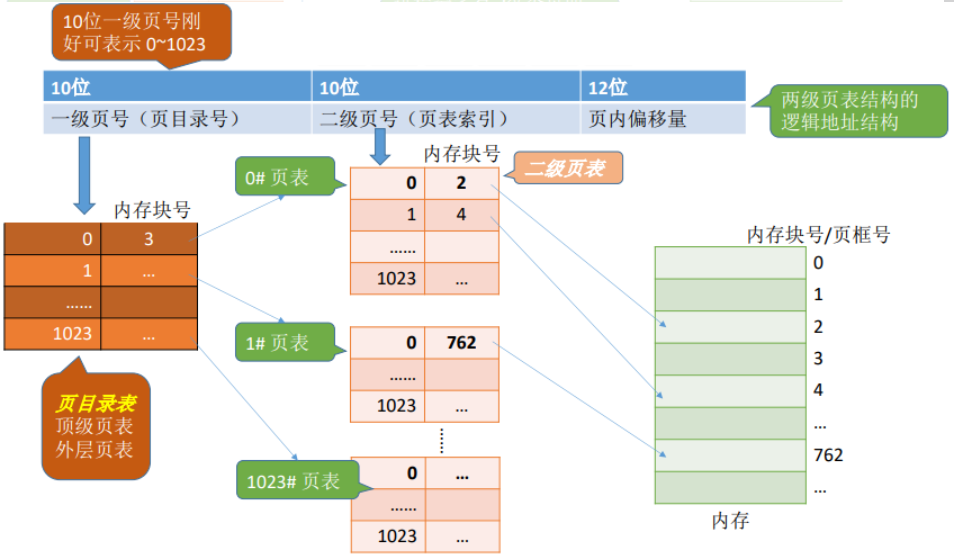

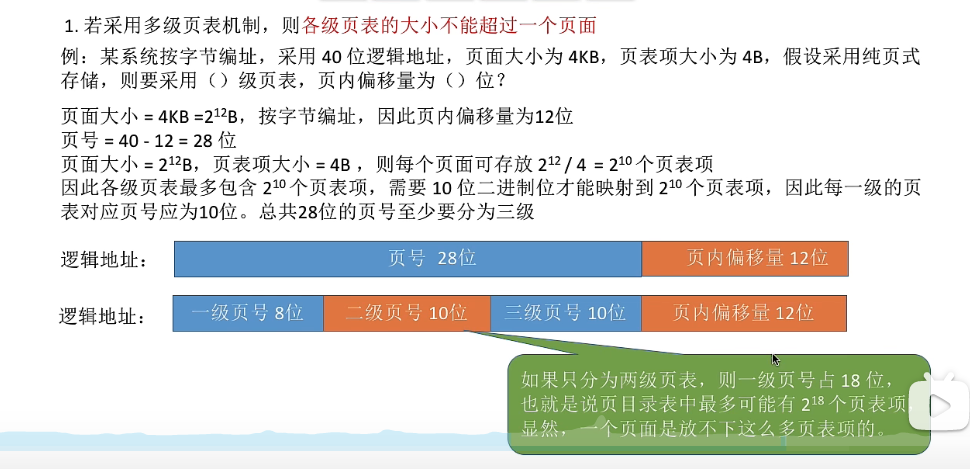

🍅1. 两级页表的原理、地址结构

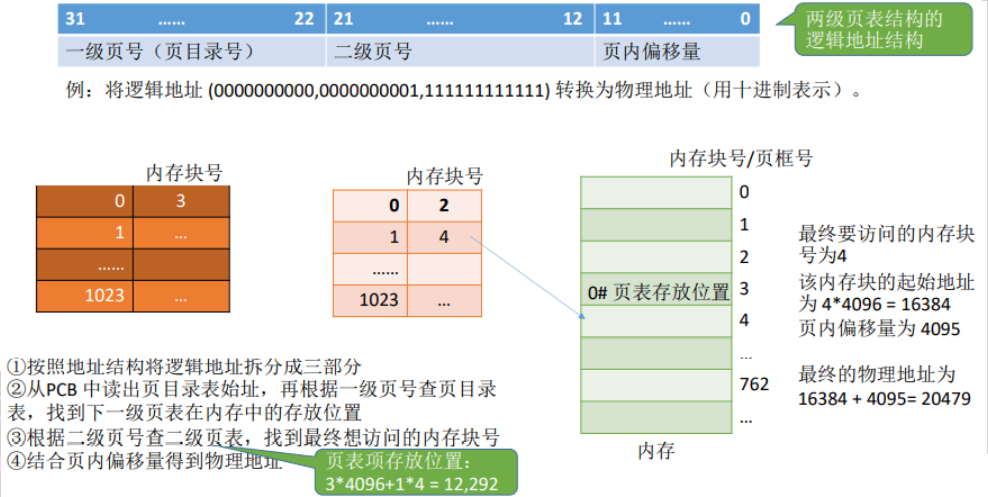

🥝 2. 如何实现地址变换

问题二:

没有必要让整个页表常驻内存,因为进程在一段时间内可能只需要访问某几个特定的页面。

🍆 1. 需要注意的几个细节

🍪基本分段存储管理方式

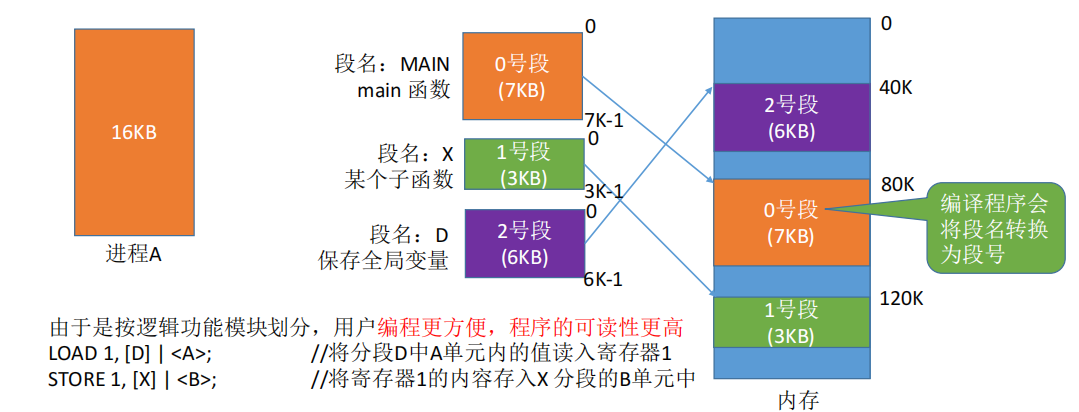

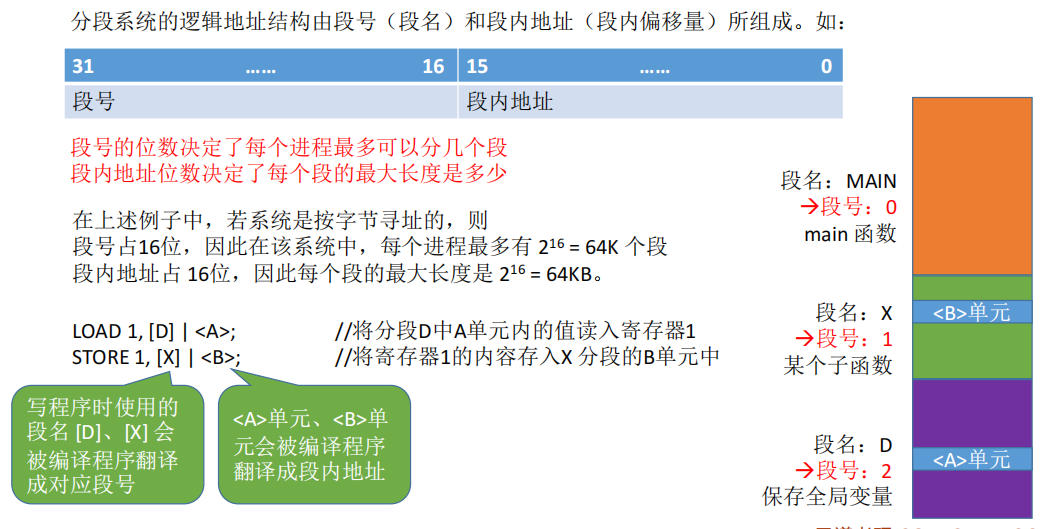

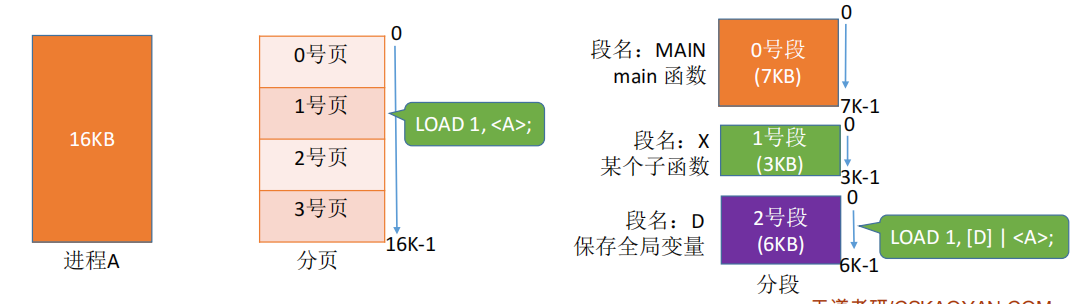

🥥 分段

- 进程的地址空间:按照程序自身的逻辑关系划分为若干个段,每个段都有一个段名(在低级语言中,程序员使用段名来编程),每段从0开始编址

- 内存分配规则:以段为单位进行分配,每个段在内存中占据连续空间,但各段之间可以不相邻

🍦段表

问题:程序分多个段,各段离散地装入内存,为了保证程序能正常运行,就必须能从物理内存中找到各个逻辑段的存放位置。为此,需为每个进程建立一张段映射表,简称“段表”。

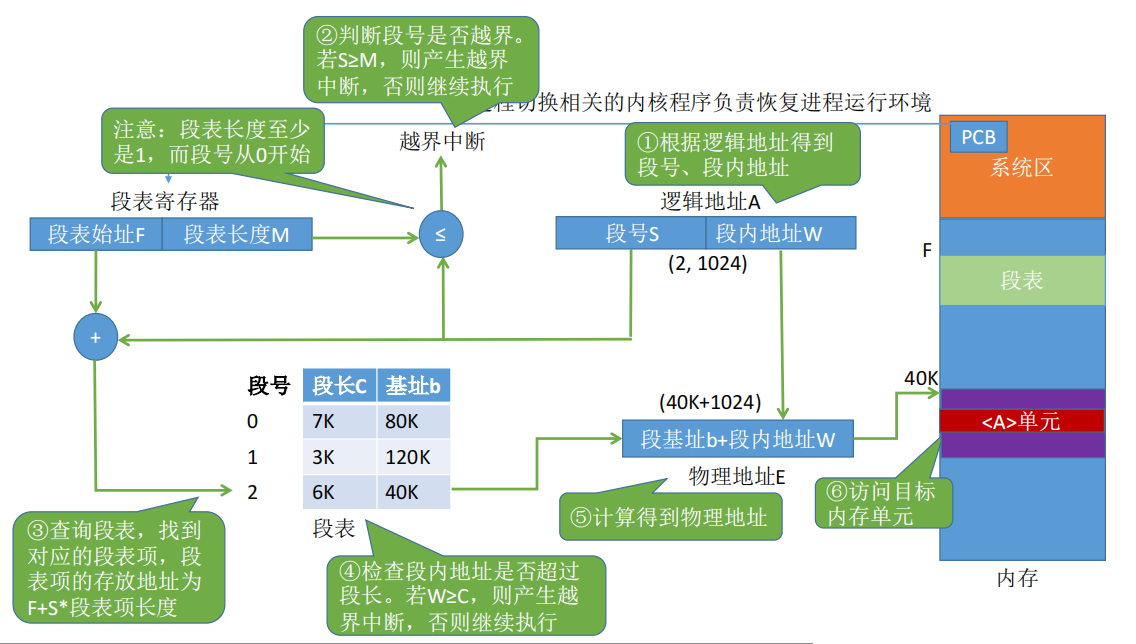

🧊地址变换

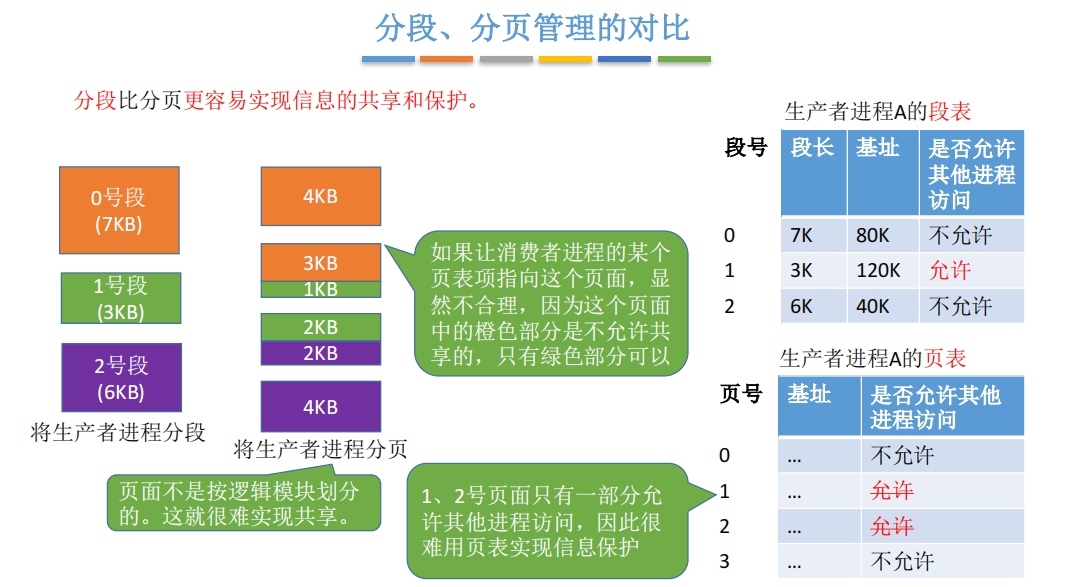

🍋 分段、分页管理的对比

- 页 是信息的物理单位。分页的主要目的是为了实现离散分配,提高内存利用率。分页仅仅是系统管理上的需要,完全是系统行为,对用户是不可见的。

- 段 是信息的逻辑单位。分段的主要目的是更好地满足用户需求。一个段通常包含着一组属于一个逻辑模块的信息。分段对用户是可见的,用户编程时需要显式地给出段名。

- 页的大小固定且由系统决定。段的长度却不固定,决定于用户编写的程序。

- 分页 的用户进程地址空间是一维的,程序员只需给出一个记忆符即可表示一个地址。

- 分段 的用户进程地址空间是二维的,程序员在标识一个地址时,既要给出段名,也要给出段内地址。

- 分段

- 访问一个逻辑地址需要几次访存?

- 分页(单级页表):第一次访存——查内存中的页表,第二次访存——访问目标内存单元。总共两次访存

- 分段:第一次访存——查内存中的段表,第二次访存——访问目标内存单元。总共两次访存与分页系统类似,分段系统中也可以引入快表机构,将近期访问过的段表项放到快表中,这样可以少一次访问,加快地址变换速度

🧀 分页、分段的优缺点分析

🧇 分段+分页=段页式管理

🌮段页式管理的逻辑地址结构

🍞段表、页表