本文验证了综合属性ASYNC_REG对寄存器位置的影响。

ASYNC_REG用于单bit信号采用双(或多)触发器实现异步跨时钟域的场合,此时所有用于同步的触发器都要标记ASYNC_REG。标记方式为:

(* ASYNC_REG = "TRUE" *) reg sync_0, sync_1;

目的是告诉综合工具布线时将这2个寄存器放在一起(即同一个SLICE中),从而减少线延迟对时序的影响。

为避免忘记标记ASYNC_REG,打开Language template -> XPM_CDC -> Single-bit Synchronizer(xpm_cdc_single),见下方代码:

xpm_cdc_single #(

.DEST_SYNC_FF(4), // DECIMAL; range: 2-10

.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.SRC_INPUT_REG(1) // DECIMAL; 0=do not register input, 1=register input

)

xpm_cdc_single_inst (

.dest_out(dest_out), // 1-bit output: src_in synchronized to the destination clock domain. This output is

// registered.

.dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain.

.src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1

.src_in(src_in) // 1-bit input: Input signal to be synchronized to dest_clk domain.

);

创建top.v,代码如下:

module top(

input src_clk,

input src_in,

input dest_clk,

output dest_out

);

xpm_cdc_single #(

.DEST_SYNC_FF(2), // DECIMAL; range: 2-10

.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.SRC_INPUT_REG(1) // DECIMAL; 0=do not register input, 1=register input

)

xpm_cdc_single_inst (

.dest_out(dest_out), // 1-bit output: src_in synchronized to the destination clock domain. This output is

// registered.

.dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain.

.src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1

.src_in(src_in) // 1-bit input: Input signal to be synchronized to dest_clk domain.

);

endmodule

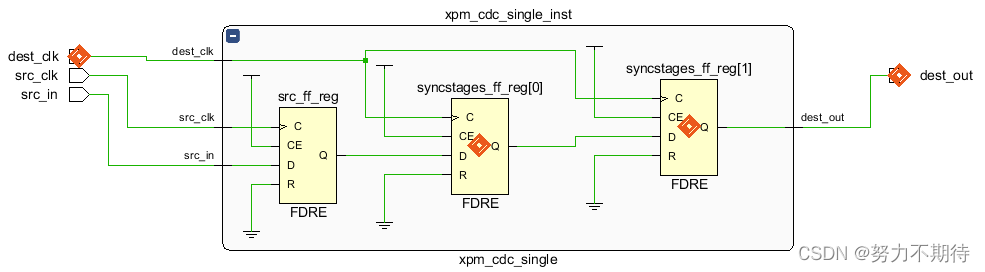

在Open Implemented Design -> Schematic中的原理图(不是综合后的原理图)为:

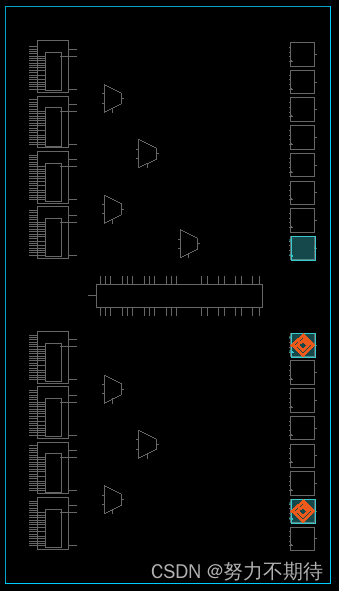

上图将dest_clk连接的2个FF MARK了,对应到Device界面的视图如下:

上图淡蓝色括住的表示一个SLICE,红色MARK对应上上图的2个寄存器FDRE,可以看出它们是在一个SLICE中的。

通过如下代码可验证ASYNC_REG是否已被标记:

set myff [get_cells -hier -filter “REF_NAME == FDRE”]

get_property ASYNC_REG $myff

执行结果如下时说明ASYNC_REG是否已被标记: