原文链接 前言

为了完成自己的毕设,得用OpenOCD作上位机,测试下RISC-V的单步调试以及GDB调试等操作,然后看了下tinyriscv-verilator的调试模块支持这些操作,所以来移植下该版本的tinyriscv,以博客进行记录。

一些基础操作这里不再赘述,不会的读者可以去看我的另一篇博客:

一、下载源码

码云链接:https://gitee.com/liangkangnan/tinyriscv/tree/verilator/

打包下载即可,解压后,将RTL添加到新建工程源码中。添加完成后,如下图所示:

可以看到 jtag 调试模块更新了,将tap、dtm、dmi以及dm模块都独立实现了。

二、移植到Aritx-7

开发板;正点原子达芬奇FPGA开发板(v1),芯片型号为 xc7a35tfgg484-1

调试器:FT4232H

2.1 添加 mmcm IP

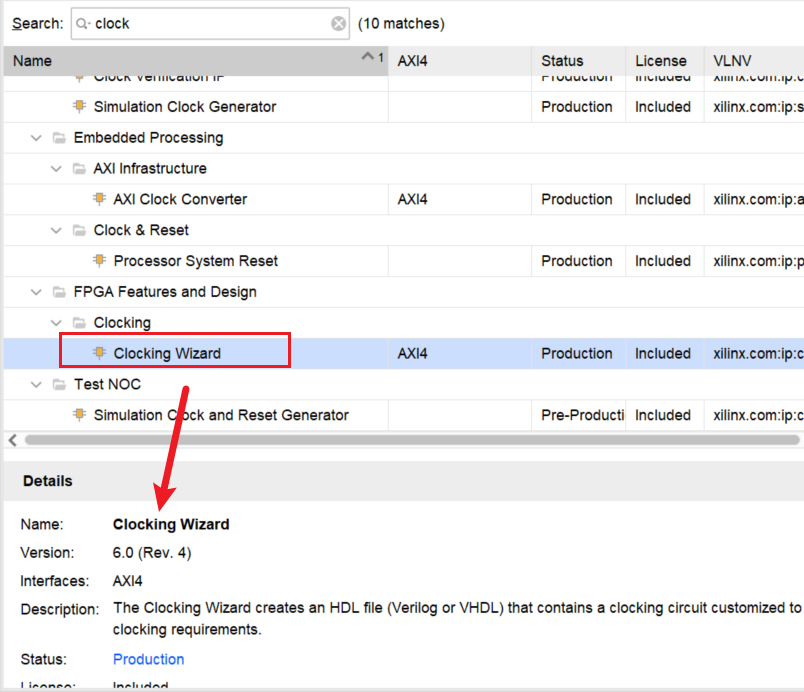

在 tinyriscv_soc_top.sv 顶层模块中例化了 mmcm IP,所以要进行添加,点击左侧导航栏中的 IP Catalog,搜索 Clocking,选择下图所示的IP:

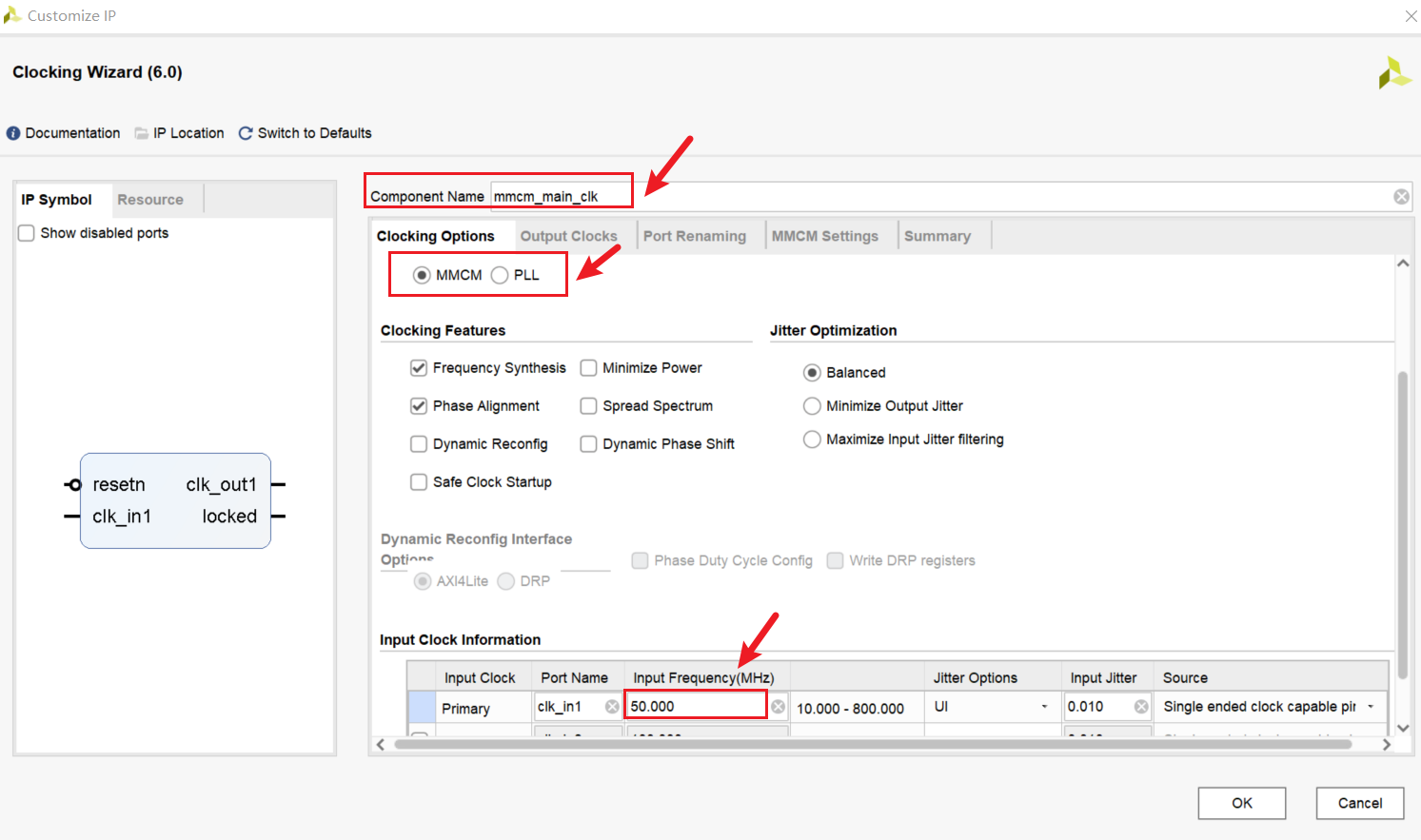

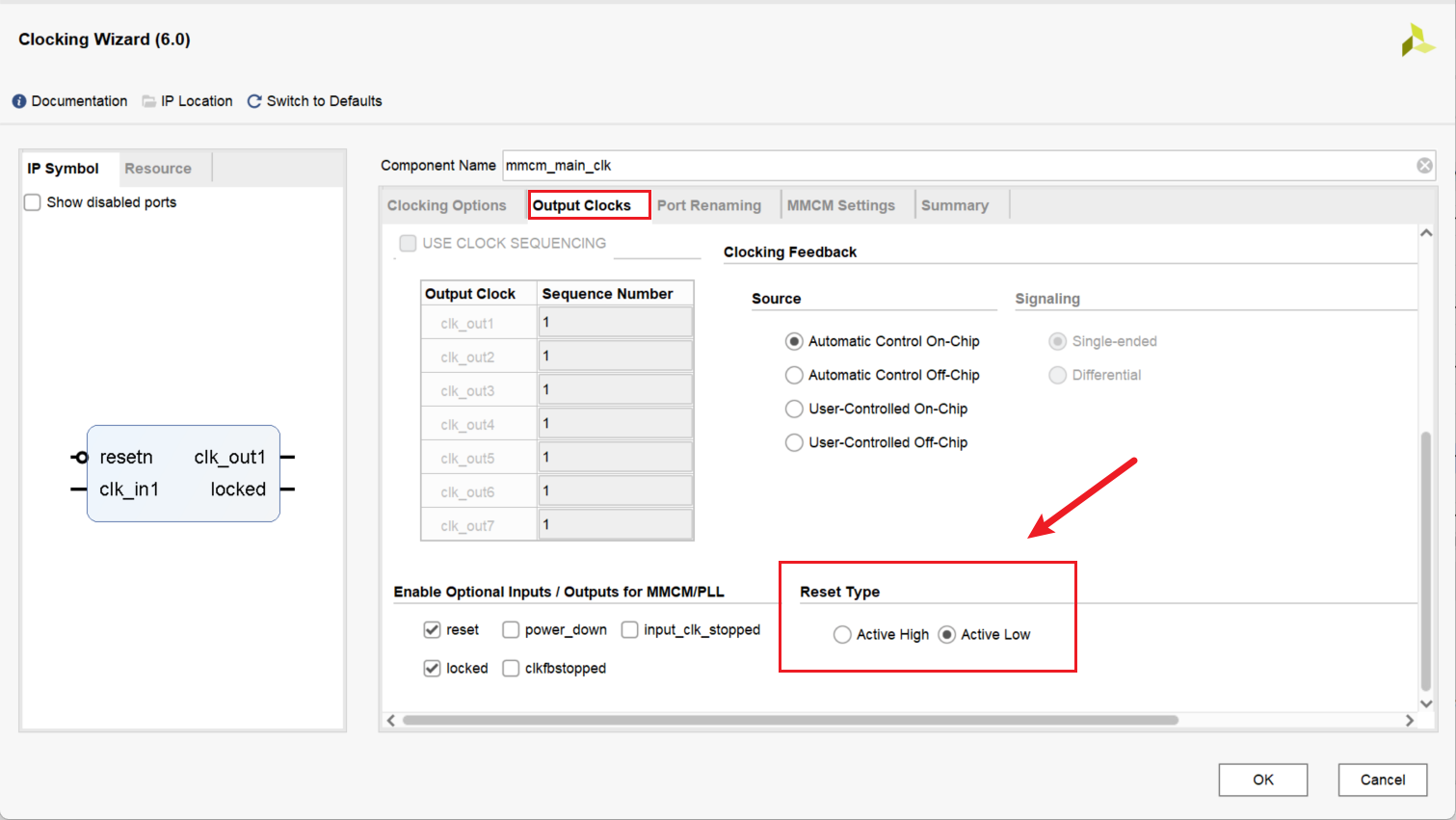

配置如下图所示;

然后点击 ok,弹出的弹窗选择 Generate。

可以看到此IP已经不再是缺失状态了。

2.2 管脚约束

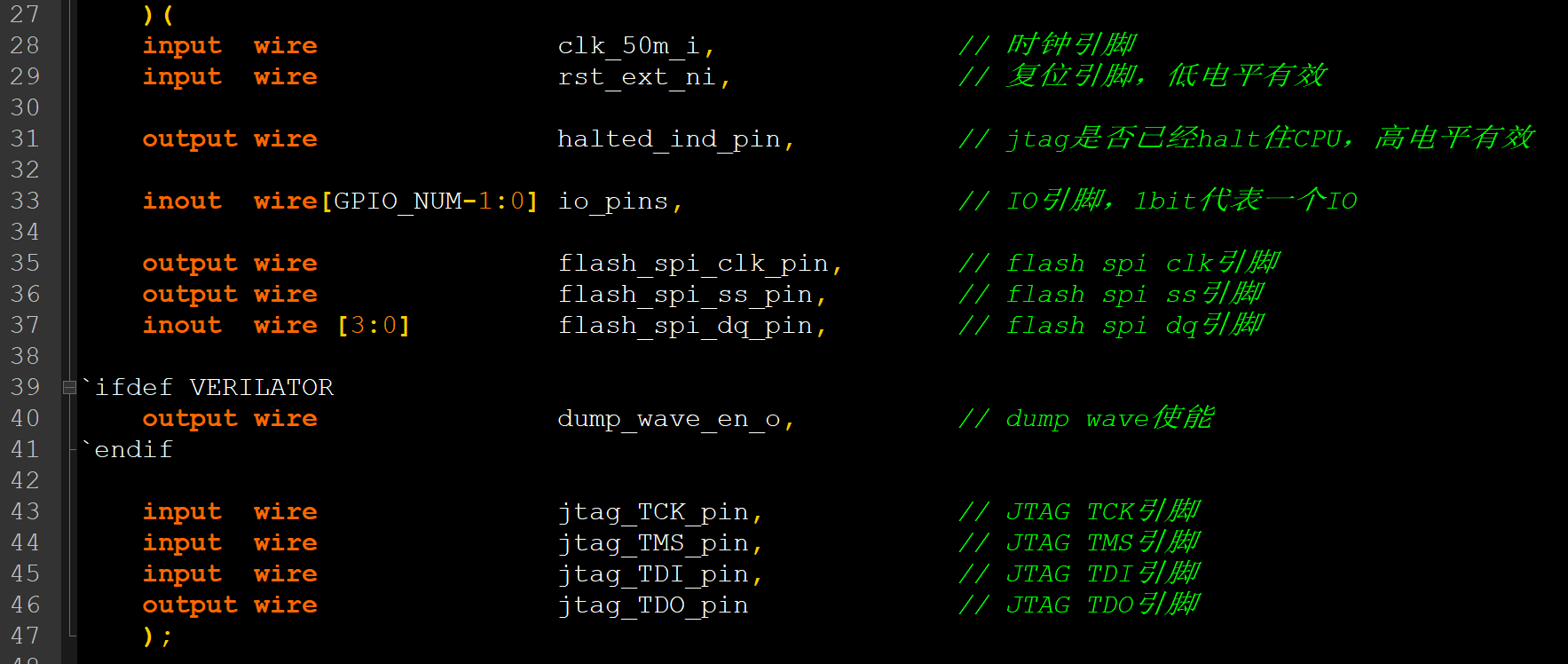

首先来看下此版本的tinyriscv的顶层接口:

可以看到和master 版本基本差不多,去掉了单独的UART Pins,将UART功能放在了GPIO复用功能中。管脚约束的话,时钟约束到板卡时钟管脚上,复位按钮约束到按钮上,halted_ind_pin 信号和 dump_wave_en_o 信号均约束到LED上,jtag、gpio和flash spi均约束到空闲IO上即可。

约束文件:

# 时钟约束50MHz,占空比50%

create_clock -period 20.000 -name sys_clk_pin -waveform {0.000 10.000} -add [get_ports clk_50m_i]

# 时钟引脚

set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports clk_50m_i]

# 复位引脚

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports rst_ext_ni]

# CPU停住指示引脚,halted_ind_pin 为1时有效,点亮led2

set_property -dict {PACKAGE_PIN V2 IOSTANDARD LVCMOS33} [get_ports halted_ind_pin]

# io_pins引脚

set_property -dict {PACKAGE_PIN F16 IOSTANDARD LVCMOS33} [get_ports {io_pins[0]}]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports {io_pins[1]}]

set_property -dict {PACKAGE_PIN F13 IOSTANDARD LVCMOS33} [get_ports {io_pins[2]}]

set_property -dict {PACKAGE_PIN E14 IOSTANDARD LVCMOS33} [get_ports {io_pins[3]}]

set_property -dict {PACKAGE_PIN H18 IOSTANDARD LVCMOS33} [get_ports {io_pins[4]}]

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {io_pins[5]}]

set_property -dict {PACKAGE_PIN H15 IOSTANDARD LVCMOS33} [get_ports {io_pins[6]}]

set_property -dict {PACKAGE_PIN H14 IOSTANDARD LVCMOS33} [get_ports {io_pins[7]}]

set_property -dict {PACKAGE_PIN G13 IOSTANDARD LVCMOS33} [get_ports {io_pins[8]}]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports {io_pins[9]}]

set_property -dict {PACKAGE_PIN AB18 IOSTANDARD LVCMOS33} [get_ports {io_pins[10]}]

set_property -dict {PACKAGE_PIN G15 IOSTANDARD LVCMOS33} [get_ports {io_pins[11]}]

set_property -dict {PACKAGE_PIN G16 IOSTANDARD LVCMOS33} [get_ports {io_pins[12]}]

set_property -dict {PACKAGE_PIN P20 IOSTANDARD LVCMOS33} [get_ports {io_pins[13]}]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports {io_pins[14]}]

set_property -dict {PACKAGE_PIN J16 IOSTANDARD LVCMOS33} [get_ports {io_pins[15]}]

# JTAG TCK引脚 PortA 0

set_property -dict {PACKAGE_PIN AA8 IOSTANDARD LVCMOS33} [get_ports jtag_TCK_pin]

create_clock -period 300.000 -name jtag_clk_pin [get_ports jtag_TCK_pin]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK_pin]

# JTAG TMS引脚 PortA 3

set_property -dict {PACKAGE_PIN AB8 IOSTANDARD LVCMOS33} [get_ports jtag_TMS_pin]

# JTAG TDI引脚 PortA 1

set_property -dict {PACKAGE_PIN Y7 IOSTANDARD LVCMOS33} [get_ports jtag_TDI_pin]

# JTAG TDO引脚 PortA 2

set_property -dict {PACKAGE_PIN Y8 IOSTANDARD LVCMOS33} [get_ports jtag_TDO_pin]

# SPI dq引脚

set_property -dict {PACKAGE_PIN F14 IOSTANDARD LVCMOS33} [get_ports {flash_spi_dq_pin[0]}]

set_property -dict {PACKAGE_PIN F18 IOSTANDARD LVCMOS33} [get_ports {flash_spi_dq_pin[1]}]

set_property -dict {PACKAGE_PIN D17 IOSTANDARD LVCMOS33} [get_ports {flash_spi_dq_pin[2]}]

set_property -dict {PACKAGE_PIN W22 IOSTANDARD LVCMOS33} [get_ports {flash_spi_dq_pin[3]}]

# SPI SS引脚

set_property -dict {PACKAGE_PIN E13 IOSTANDARD LVCMOS33} [get_ports flash_spi_ss_pin]

# SPI CLK引脚

set_property -dict {PACKAGE_PIN H22 IOSTANDARD LVCMOS33} [get_ports flash_spi_clk_pin]

#SPI 相关设置

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]

2.3 综合实现

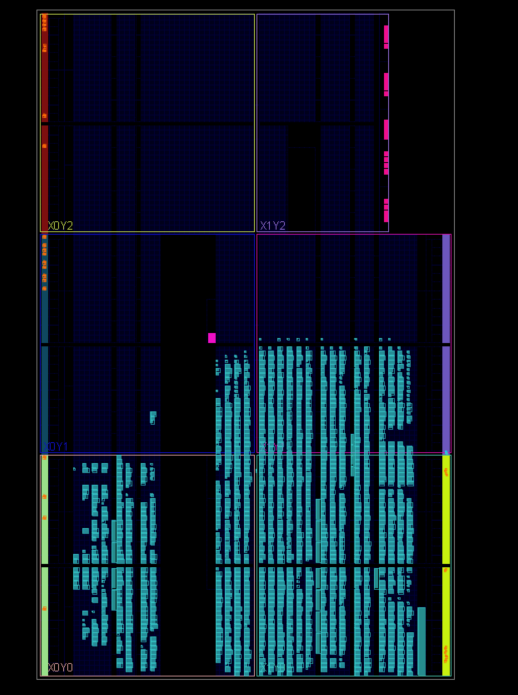

管脚约束好后,进行综合实现,版图如下:

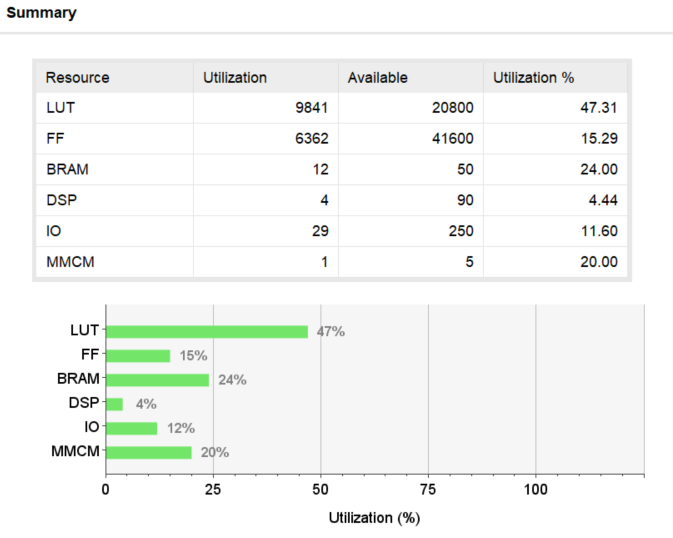

资源利用率;

三、简单测试

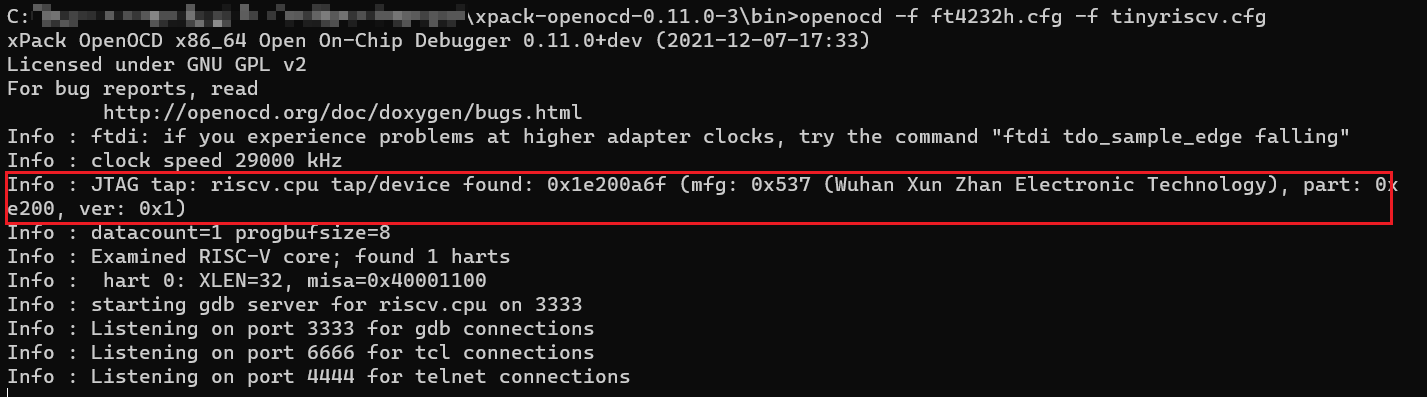

生成比特流下载到开发板上,然后通过OpenOCD进行连接。

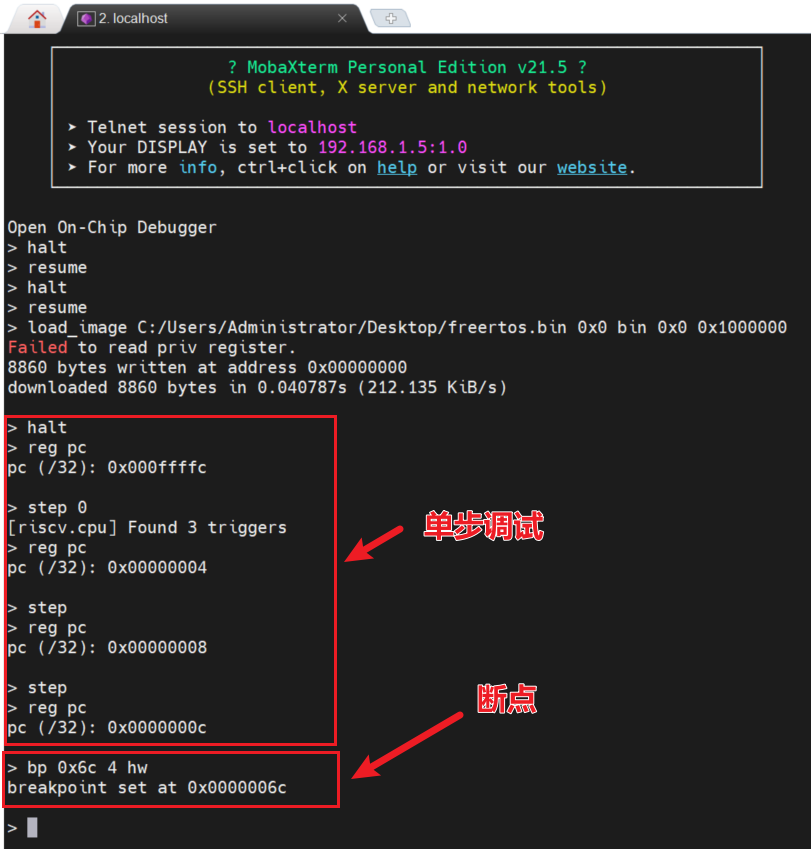

可以看到已经成功连接到了。再登录终端尝试单步调试和断点:

原文链接