计算机的运算方法——第六章

一、无符号数和有符号数

1. 无符号数

特点:保存时只有数值位,没有符号位。假如使用寄存器保存无符号数,那么:寄存器的位数反映了无符号数的表示范围。例如:

- 寄存器为 8 位,无符号数表示范围为 0~255

- 寄存器为16位,无符号数表示范围为 0~65535

2. 有符号数

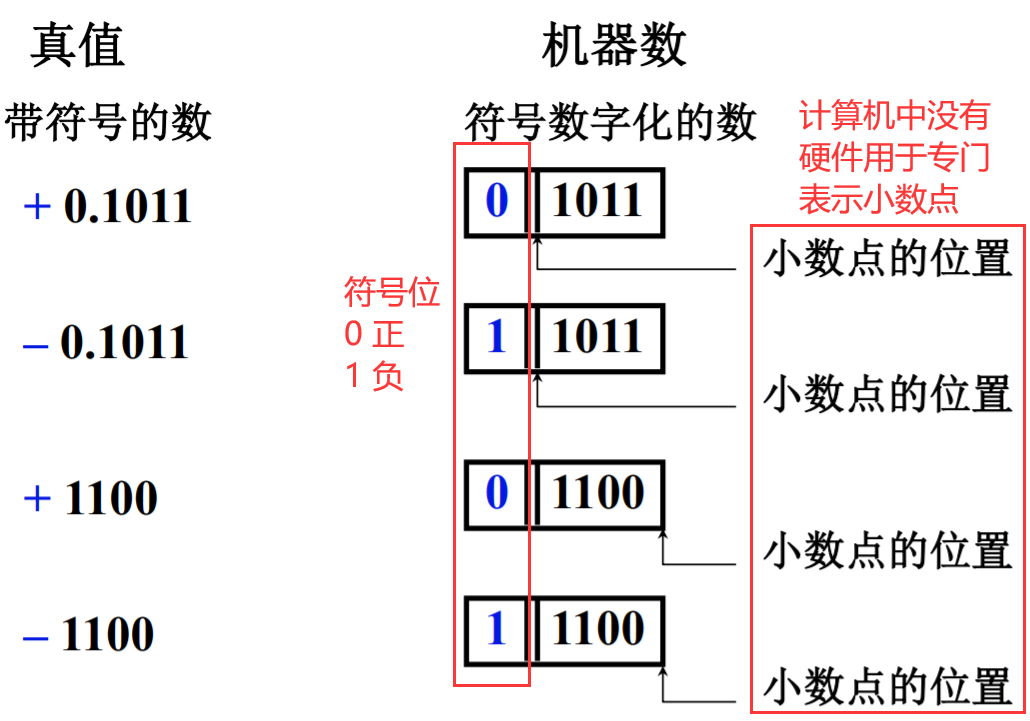

1. 机器数与真值

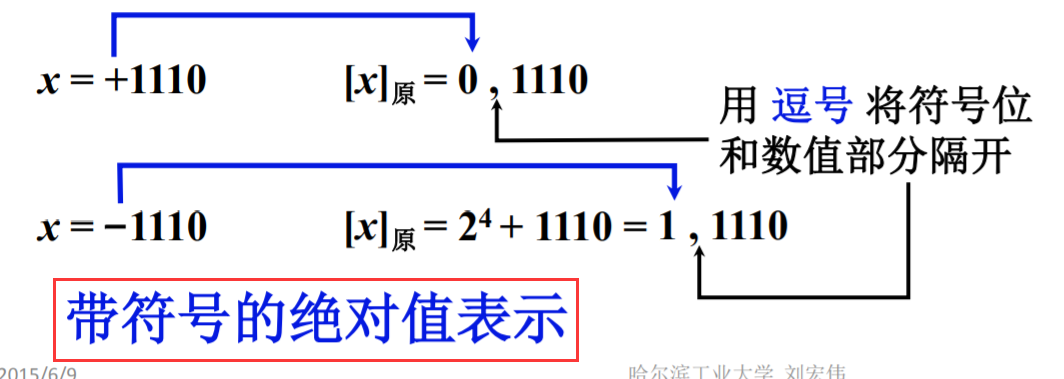

2. 原码表示法

1. 整数

定义如下:

[

x

]

原

=

{

0

,

x

2

n

>

x

≥

0

2

n

−

x

0

≥

x

>

−

2

n

x

为

真

值

,

n

为

整

数

的

位

数

[x]_原 = \begin{cases} 0,x \qquad 2^n > x \geq 0\\ 2^n-x \quad 0 \geq x > -2^n\end{cases} \qquad x为真值,n为整数的位数

[x]原={0,x2n>x≥02n−x0≥x>−2nx为真值,n为整数的位数

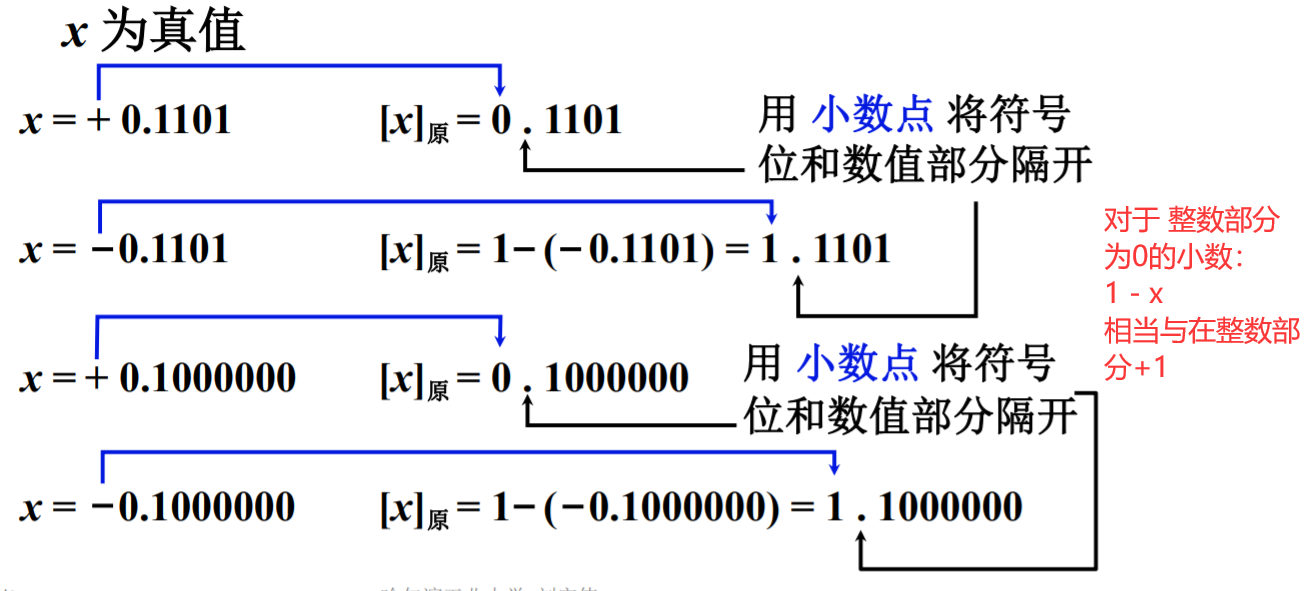

2. 小数

定义如下:

[

x

]

原

=

{

x

1

>

x

≥

0

1

−

x

0

≥

x

>

−

1

[x]_原 = \begin{cases} x \qquad\quad 1>x\geq0 \\ 1-x \quad 0 \geq x > -1 \end{cases}

[x]原={x1>x≥01−x0≥x>−1

3. 小结

| 数值类型 | 真值 | 原码表示 | 计算公式 | 变换特点 |

|---|---|---|---|---|

| 整数 | x (正数) | 0,x | 0,x | 在最左侧加一个符号位表示符号 |

| x (负数) | 1,x | 2^n-x | ||

| 整数部分为0的小数(纯小数) 如0.2 | x (正数) | x | x | 整数部分变成符号位(个位变符号位) |

| -0.1101 | 1.1101 | 1-x |

原码的特点:简单、直观。但是用原码有如下问题:

4. 例题

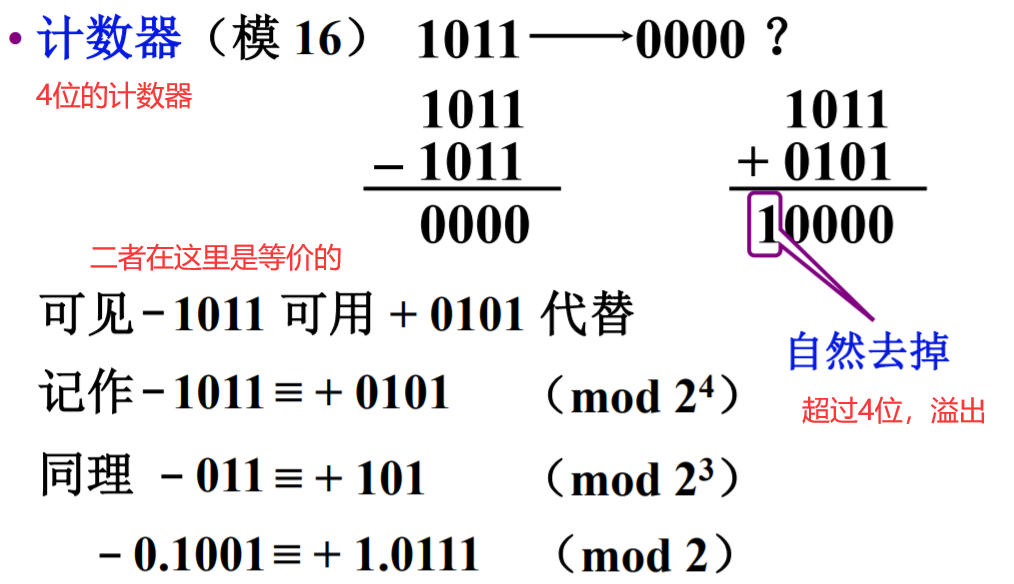

3. 补码表示法

1. 补的概念

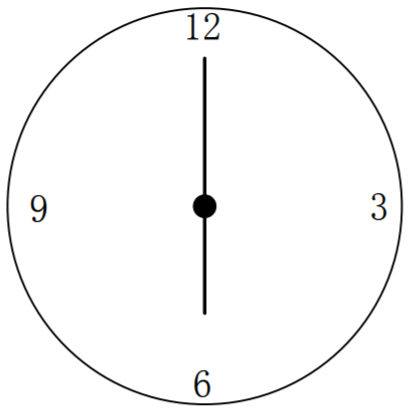

现在,我们希望:分针由 6 指向 3,有两种实现方案

- 逆时针转动指针,转动3个单位,记作==-3==

- 顺时针转动指针,转动9个单位,记作==+9==

在这里,-3和==+9是等价的,记作 − 3 ≡ 9 ( m o d 12 ) -3 \equiv 9 \,(mod \,12) −3≡9(mod12),称+9是-3以12为模的补数==。

这里有两个结论:

- 一个负数加上“模”即得该负数的补数(正数)

- 一个正数和一个负数互为补数时, 它们绝对值之和即为 “模” 数

2. 正数的补数即为其本身

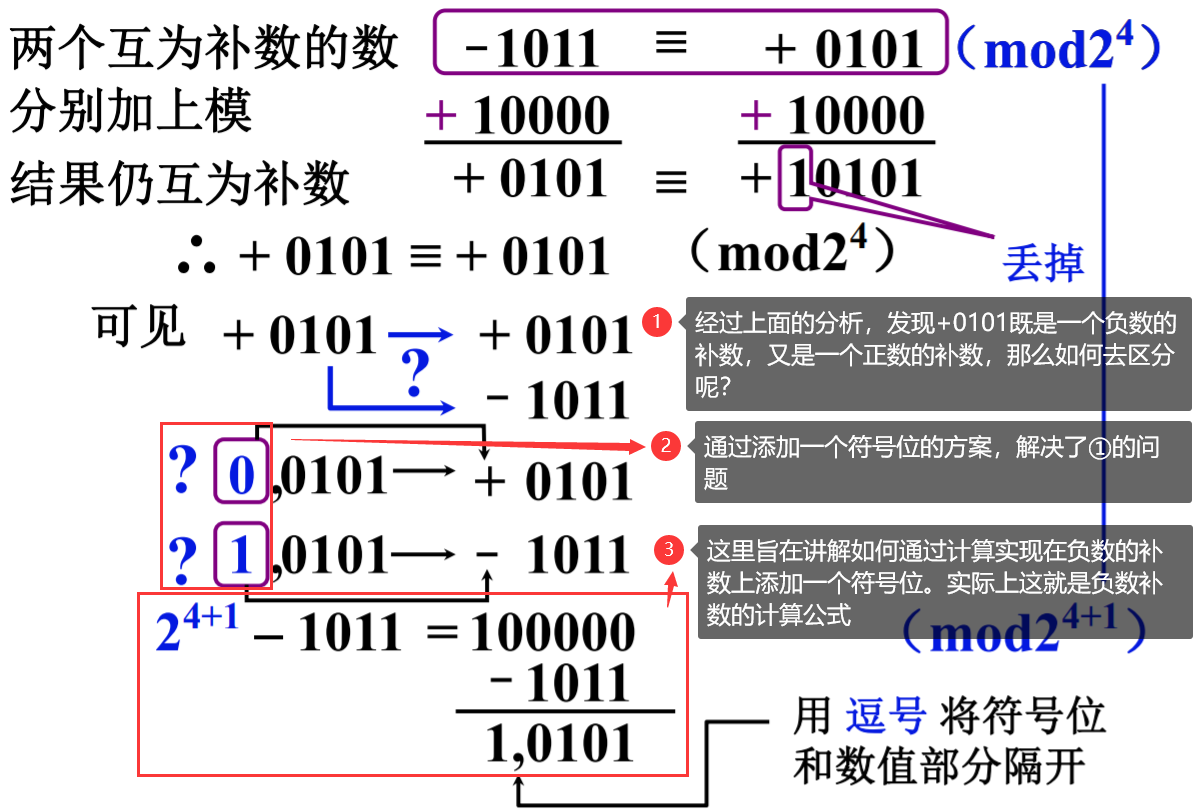

3. 补码定义

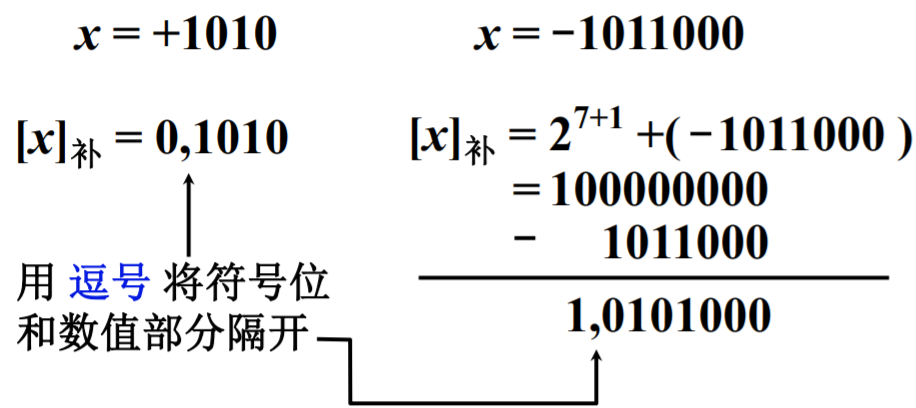

1. 整数

公式如下:

[

x

]

补

=

{

0

,

x

2

n

>

x

≥

0

2

n

+

1

+

x

0

>

x

≥

−

2

n

(

m

o

d

2

n

+

1

)

x

为

真

值

,

n

为

整

数

的

位

数

[x]_补=\begin{cases} 0,x \qquad 2^n>x\geq0 \\ 2^{n+1}+x \quad 0>x\geq -2^n \quad(mod \, 2^{n+1})\end{cases} \qquad x为真值,n为整数的位数

[x]补={0,x2n>x≥02n+1+x0>x≥−2n(mod2n+1)x为真值,n为整数的位数

2. 小数

公式如下:

[

x

]

补

=

{

x

1

>

x

≥

0

2

+

x

0

>

x

≥

−

1

(

m

o

d

2

)

x

为

真

值

[x]_补=\begin{cases} x \qquad 1>x\geq0 \\ 2+x \quad 0>x\geq-1 \quad (mod \, 2) \end{cases} \qquad x为真值

[x]补={x1>x≥02+x0>x≥−1(mod2)x为真值

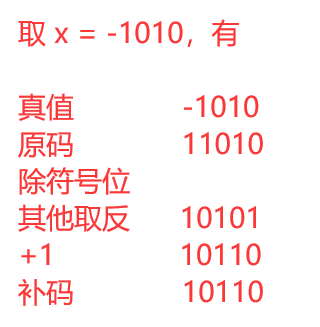

4. 求补码的快捷方式

当真值为负时,补码的计算方法:

- 原码:除符号位外,其他每位取反

- 取反后,末位+1

同时,当真值为负时,通过补码计算原码的方法:原码 可用 补码除符号位外 每位取反,末位加 1 求得

4. 反码表示法

1. 反码定义

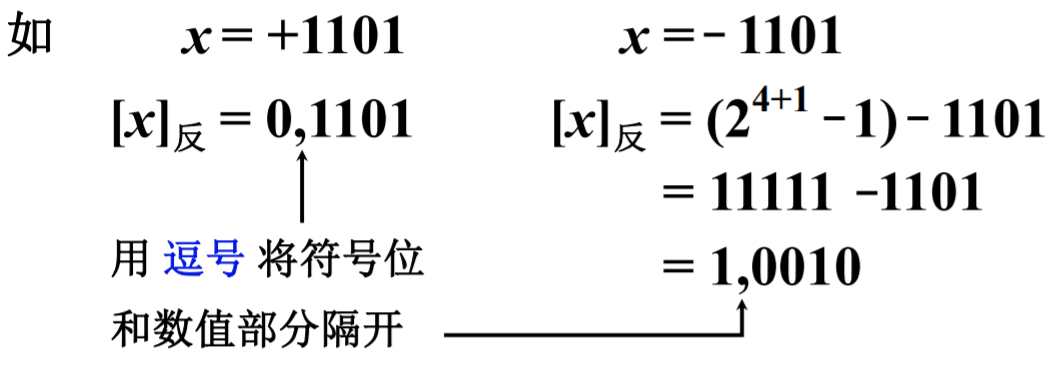

1. 整数

[ x ] 反 = { 0 , x 2 n > x ≥ 0 ( 2 n + 1 − 1 ) + x 0 ≥ x > − 2 n ( m o d 2 n + 1 − 1 ) x 为 真 值 , n 为 整 数 的 位 数 [x]_反= \begin{cases} 0,x \qquad\quad\quad\quad 2^n>x \geq 0 \\ (2^{n+1}-1)+x \quad 0 \geq x>-2^n \quad (mod \, 2^{n+1}-1) \end{cases} \qquad x为真值,n为整数的位数 [x]反={0,x2n>x≥0(2n+1−1)+x0≥x>−2n(mod2n+1−1)x为真值,n为整数的位数

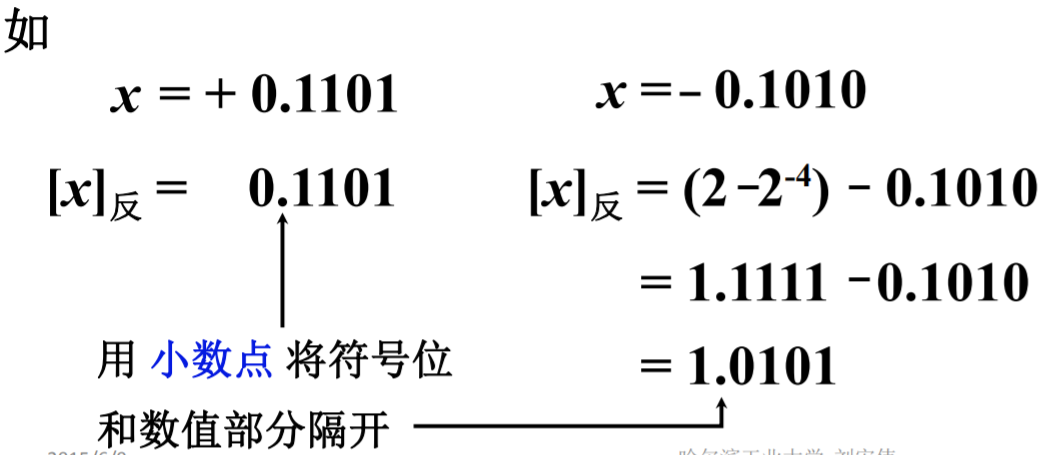

2. 小数

[ x ] 反 = { x 1 > x ≥ 0 ( 2 − 2 − n + x ) 0 ≥ x > − 1 ( m o d 2 − 2 − n ) x 为 真 值 , n 为 小 数 的 位 数 [x]_反= \begin{cases} x \qquad\quad\quad 1>x \geq 0 \\ (2-2^{-n}+x) \quad 0 \geq x>-1 \quad (mod \, 2-2^{-n}) \end{cases} \qquad x为真值,n为小数的位数 [x]反={x1>x≥0(2−2−n+x)0≥x>−1(mod2−2−n)x为真值,n为小数的位数

2. 例子

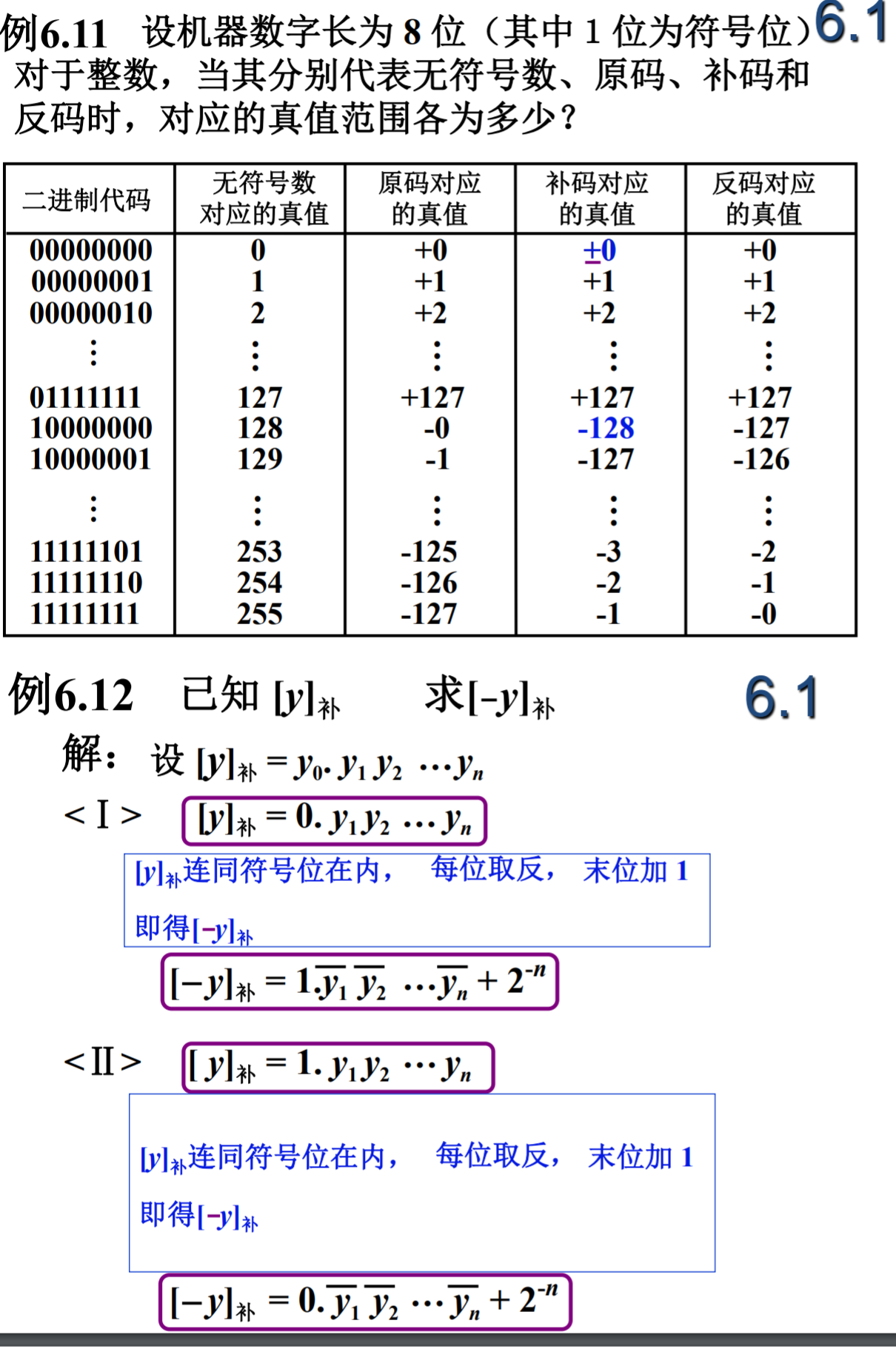

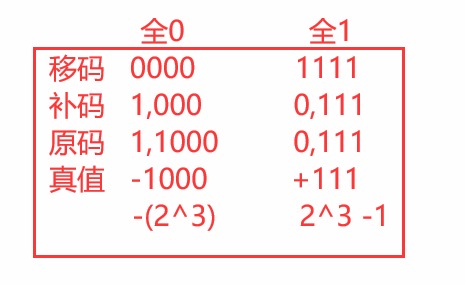

5. 原码、补码、反码小结

- 最高位为符号位,用指定符号将 数值部分 和 符号位 隔开

- 整数用 ,

- 小数用 .

- 对于正数:

- 原码 = 补码 = 反码

- 真值变原码:最左侧加符号位 0

- 对于负数,符号位为1,其数值部分

- 原码除符号位外每位取反,末位+1 ----> 补码

- 原码除符号位外每位取反 ----> 反码

例题

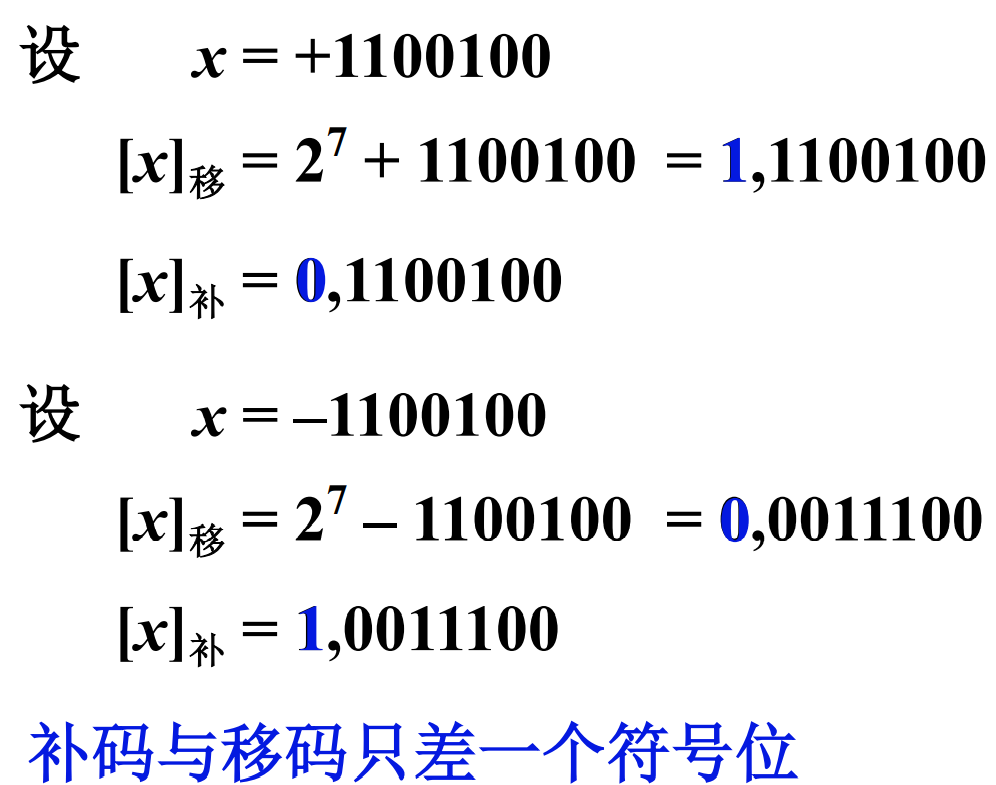

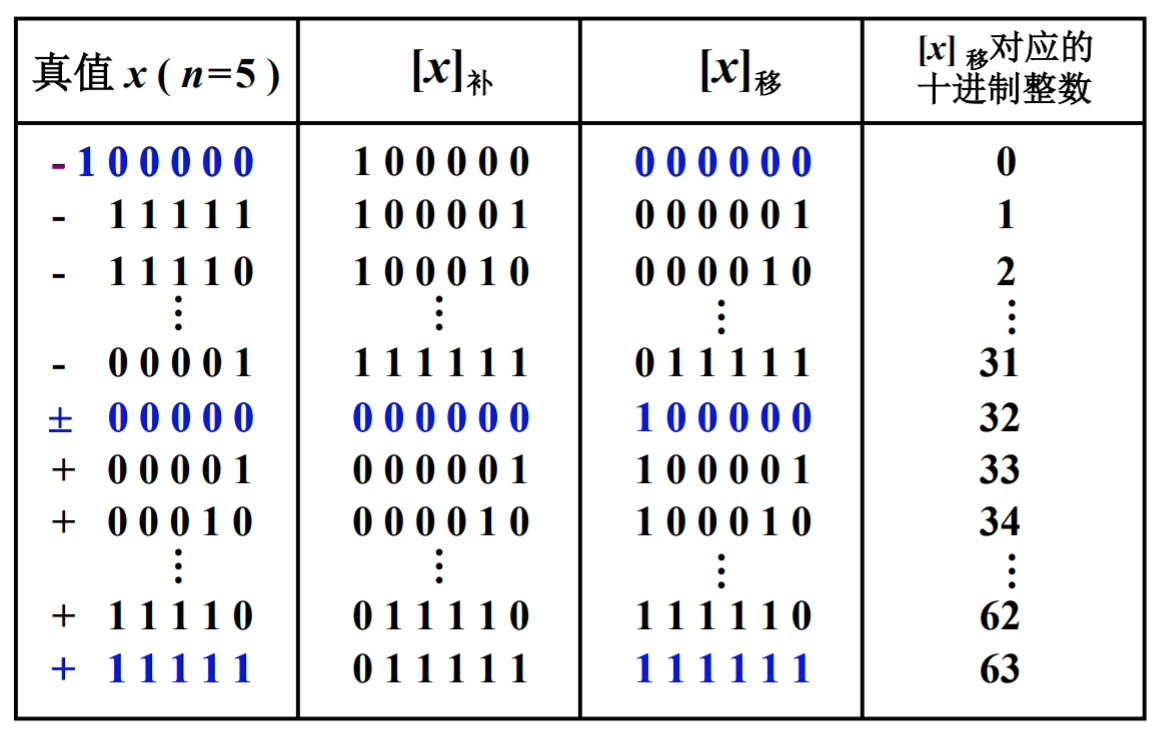

6. 移码表示法

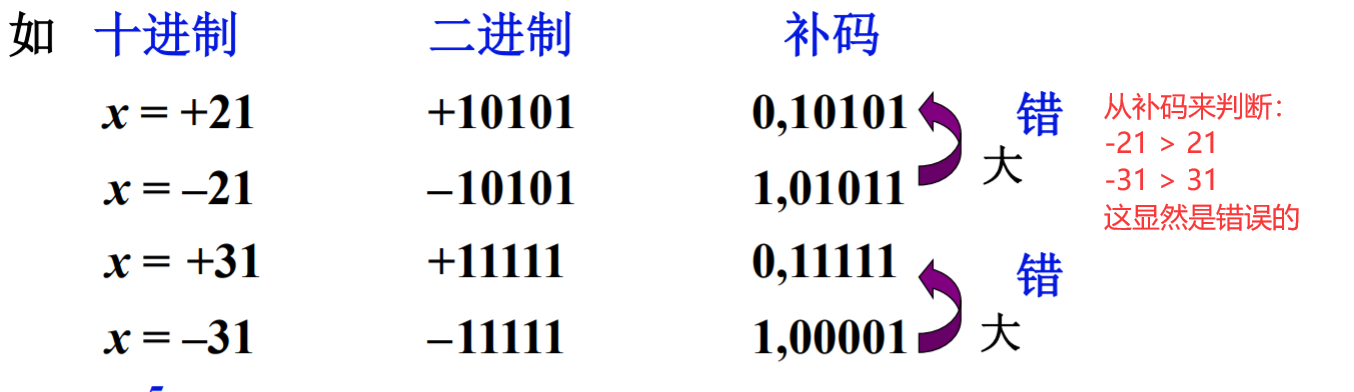

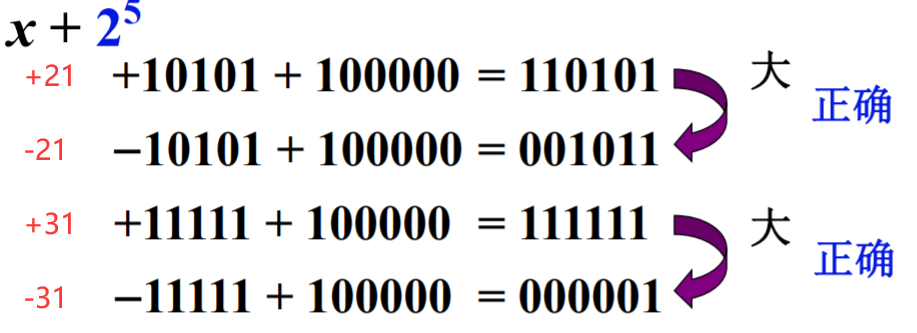

原因在于使用补码难以直接比较数的大小,如下图:

1. 定义

公式如下:

x

移

=

2

n

+

x

(

2

n

>

x

≥

−

2

n

)

x

为

真

值

,

n

为

整

数

的

位

数

x_移=2^n+x \quad (2^n>x \geq -2^n) \qquad x为真值,n为整数的位数

x移=2n+x(2n>x≥−2n)x为真值,n为整数的位数

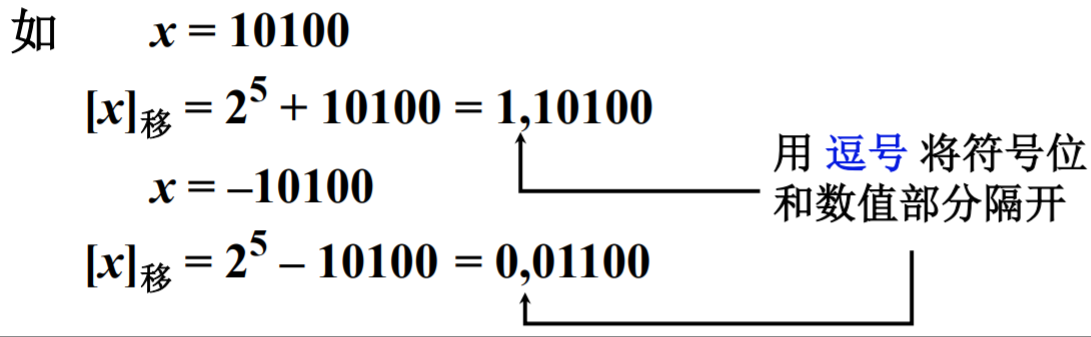

注意,移码只定义了整数。移码表示例子:

2. 移码和补码的比较

3. 真值、补码和移码的对照表

4. 移码的特点

- 用移码表示浮点数的阶码(整数),能方便地判断浮点数的阶码大小

- [ + 0 移 ] = [ − 0 ] 移 [+0_移]=[-0]_移 [+0移]=[−0]移,即0的移码是唯一的:1,n个0

- 移码全0表示的是最小值== − ( 2 n − 1 ) -(2^{n-1}) −(2n−1)。全1时表示最大值 2 n − 1 2^n-1 2n−1==。如下图

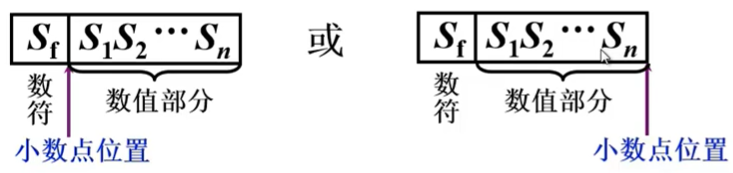

二、数的定点表示和浮点表示

计算机中,没有为小数点设置专门的存储逻辑。小数点的位置是以约定的方式给出的。当约定小数点在某一指定点时,这就是定点表示。

1. 定点表示

| 表示类型 | 小数定点机 | 整数定点机 | ||

|---|---|---|---|---|

| 表示范围(二进制) | 表示范围(十进制) | 表示范围(二进制) | 表示范围(十进制) | |

| 原码 | 1.111...1 ~ 0.111...1 (n个1或0) | -(1- 2^(-n)) ~ +(1- 2^(-n)) | 1,111...1 ~ 0,111...1 (n个1或0) | -(2^n -1) ~ +(2^n -1) |

| 补码 | 1.000...0 ~ 0.111...1 (n个1或0) | -1 ~ +(1- 2^(-n)) | 1,000...0 ~ 0,111...1 (n个1或0) | -2^n ~ +(2^n -1) |

| 反码 | 0.000...0 ~ 1.111...1 (n个1或0) | -(1- 2^(-n)) ~ +(1- 2^(-n)) | 0,000...0 ~ 1,111...1 (n个1或0) | -(2^n -1) ~ +(2^n -1) |

2. 浮点表示

- 为什么在计算机中要引入浮点数表示

- 浮点表示的格式是什么

- 尾数和阶码的基值必须是2吗?基值的影响?

- 表数范围与精度和哪些因素有关

- 为什么要引入规格化表示

- 目前浮点数表示格式的标准是什么

为什么在计算机中要引入浮点数表示?

- 编程困难,程序员要调节小数点的位置

- 数的表示范围小,为了能表示两个大小相差很大的数据,需要很长的机器字长

- 数据存储单元的利用率往往很低

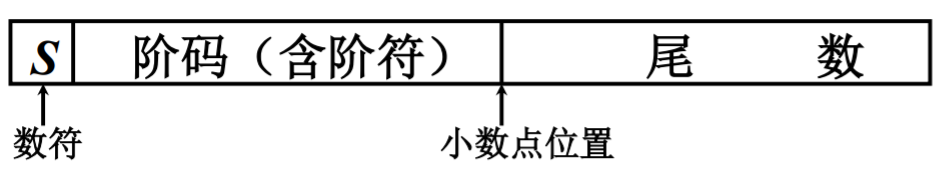

1. 浮点数表示形式

N = S × r j S 尾 数 , j 阶 码 , r 尾 数 的 基 值 N=S \times r^j \qquad S\,尾数,j\,阶码,r\,尾数的基值 N=S×rjS尾数,j阶码,r尾数的基值

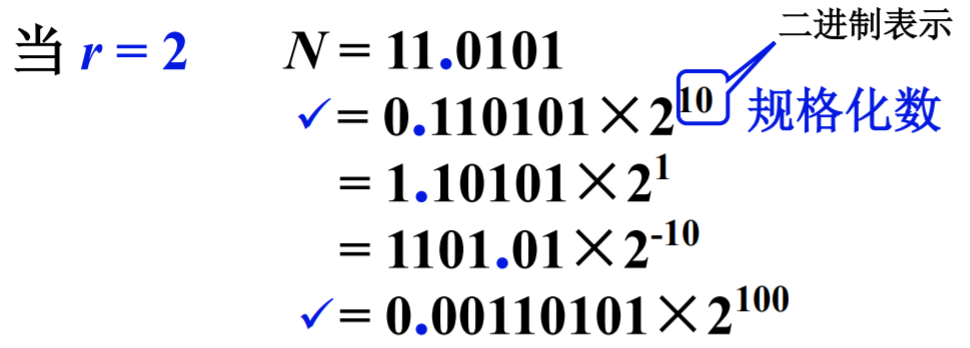

计算机中 r 取 2、4、8、16 等。如下例:

计算机中规定:(图中√标记的符合计算机要求)

- 尾数S 取纯小数(可正可负),并称尾数最高位为1的浮点数为规格化数(这里最高位指的是尾数的真值部分,即小数点后第1位)

- 阶码j 取整数(可正可负)

- 首先,我们以十进制作为切入点,我们知道

12138

=

1.2138

×

1

0

4

12138 = 1.2138\times10^4

12138=1.2138×104,此时:

- r = 10 , j = 4 r=10,j=4 r=10,j=4, r r r正好取的进制数

- j = 4 j=4 j=4在这里表示小数点向左移动四位。假如 j = − 4 j=-4 j=−4,那么就表示 小数点向右移动四位

- 那么,接下来理解:二进制取基数

r

=

2

r=2

r=2的情况。对比十进制的例子,其实当

r

=

2

r=2

r=2时,

r

j

r_j

rj代表的同样是小数点的偏移情况

- j > 0 j>0 j>0:代表小数点向左偏移

- j < 0 j<0 j<0:代表小数点向右偏移

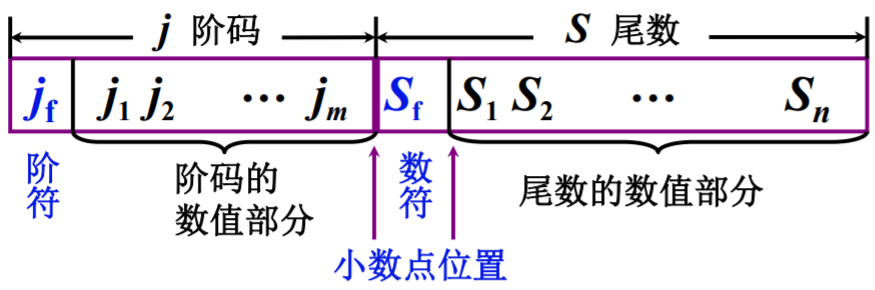

- S f S_f Sf:浮点数的符号

- j f j_f jf:阶码的符号

- n:其位数反映浮点数的精度(纯小数所能表示的最大位数)

- m:其位数反映浮点数的表示范围

- j f 和 m j_f 和 m jf和m共同表示小数点的实际位置

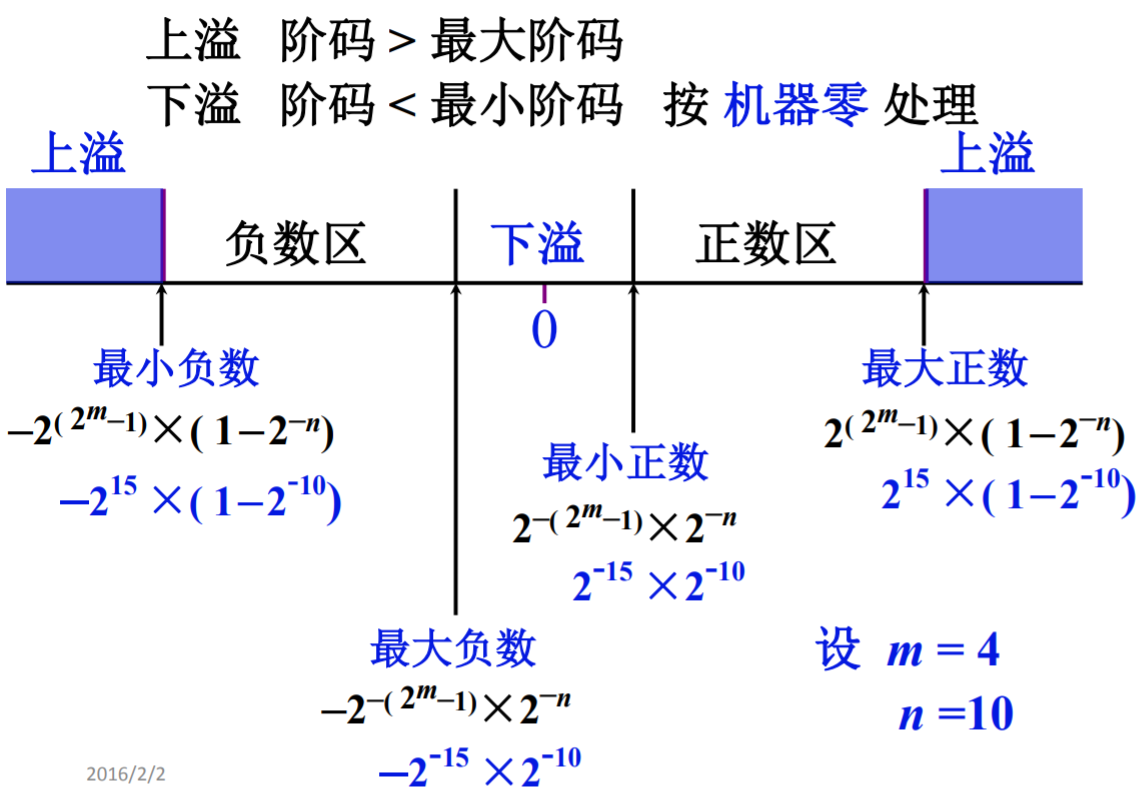

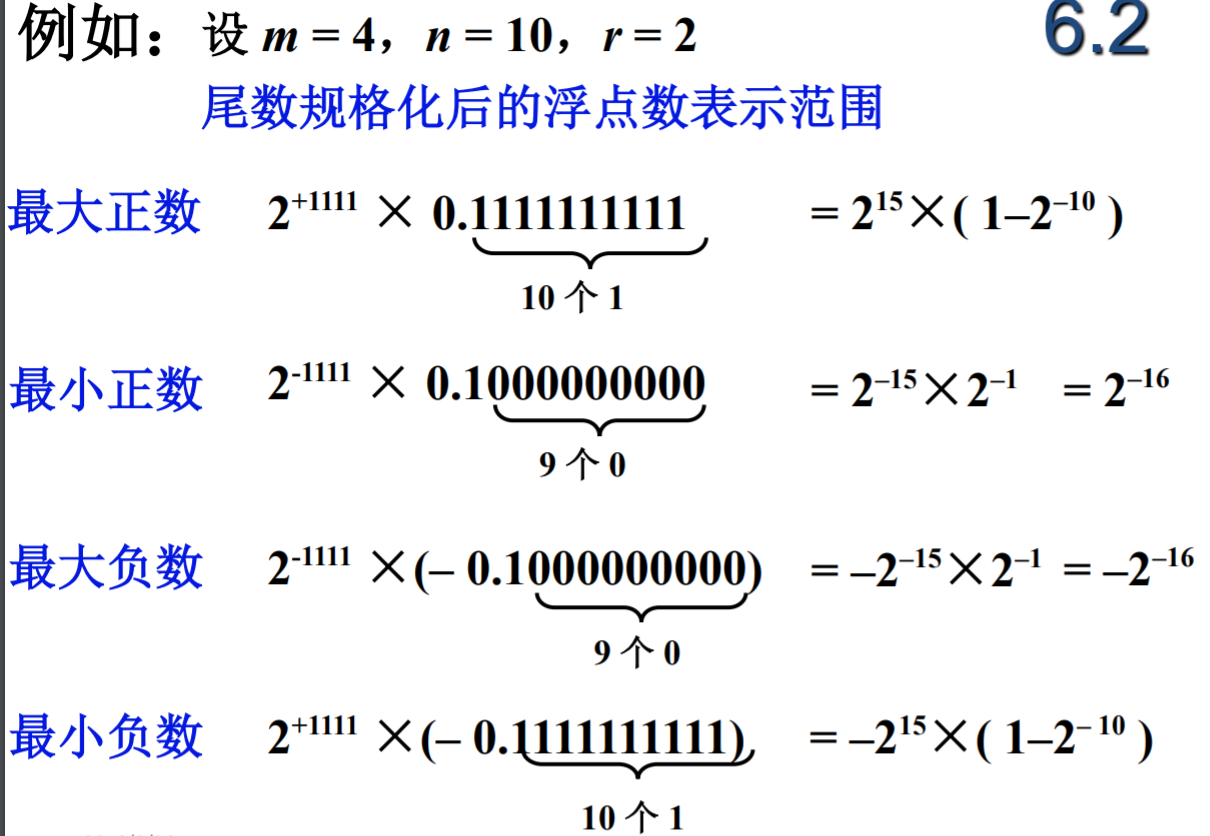

2. 浮点数的表示范围

-

发生下溢:直接当机器零处理

-

发生上溢:进行出错处理

-

阶码最小值分析:

- 阶码符号位 j f j_f jf 取负数

- 阶码m位全取 1

- 原码表示就是: 1 , 111..1 ( m 个 1 ) 1,111..1(m个1) 1,111..1(m个1)。十进制表示就是 2 − ( 2 m − 1 ) 2^{-(2^m -1)} 2−(2m−1)

-

阶码最大值分析:

- 阶码符号位 f j f_j fj 取正数

- 阶码m位全取 1

- 原码表示就是: 0 , 111..1 ( m 个 1 ) 0,111..1(m个1) 0,111..1(m个1)。十进制表示就是 2 ( 2 m − 1 ) 2^{(2^m -1)} 2(2m−1)

- 最小负数

- 尾数数值部分取最大值,符号位

S

f

S_f

Sf 取负(实际上就是尾数的最小值)

- 原码表示就是: 1.111..1 ( n 个 1 ) 1.111..1(n个1) 1.111..1(n个1)

- 十进制表示就是: − ( 1 − 2 − n ) -(1-2^{-n}) −(1−2−n)

- 阶码取最大值

- 十进制表示: − 2 ( 2 m − 1 ) × ( 1 − 2 − n ) -2^{(2^{m-1})} \times (1- 2^{-n}) −2(2m−1)×(1−2−n)

- 尾数数值部分取最大值,符号位

S

f

S_f

Sf 取负(实际上就是尾数的最小值)

- 最大负数

- 尾数数值部分取最小值,符号位

S

f

S_f

Sf 取负

- 原码表示就是: 1.000..1 ( n − 1 个 0 ) 1.000..1(n-1个0) 1.000..1(n−1个0)

- 十进制表示就是: − 2 − n -2^{-n} −2−n

- 阶码取最小值

- 十进制表示: − 2 − ( 2 m − 1 ) × 2 − n -2^{-(2^m -1)} \times 2^{-n} −2−(2m−1)×2−n

- 尾数数值部分取最小值,符号位

S

f

S_f

Sf 取负

- 最小正数

- 尾数数值部分取最小值,符号位

S

f

S_f

Sf 取正

- 原码表示就是: 0.000..1 ( n − 1 个 0 ) 0.000..1(n-1个0) 0.000..1(n−1个0)

- 十进制表示就是: + 2 − n +2^{-n} +2−n

- 阶码取最小值

- 十进制表示就是: 2 − ( 2 m − 1 ) × 2 − n 2^{-(2^m -1)} \times 2^{-n} 2−(2m−1)×2−n

- 尾数数值部分取最小值,符号位

S

f

S_f

Sf 取正

- 最大正数

- 尾数数值部分取最大值,符号位 S_f 取正

- 原码表示就是: 0 , 111..1 ( n 个 1 ) 0,111..1(n个1) 0,111..1(n个1)

- 十进制表示就是: + ( 1 − 2 − n ) +(1-2^{-n}) +(1−2−n)

- 阶码取最大值

- 十进制表示就是: 2 2 m − 1 × ( 1 − 2 − n ) 2^{2^m -1} \times (1-2^{-n}) 22m−1×(1−2−n)

- 尾数数值部分取最大值,符号位 S_f 取正

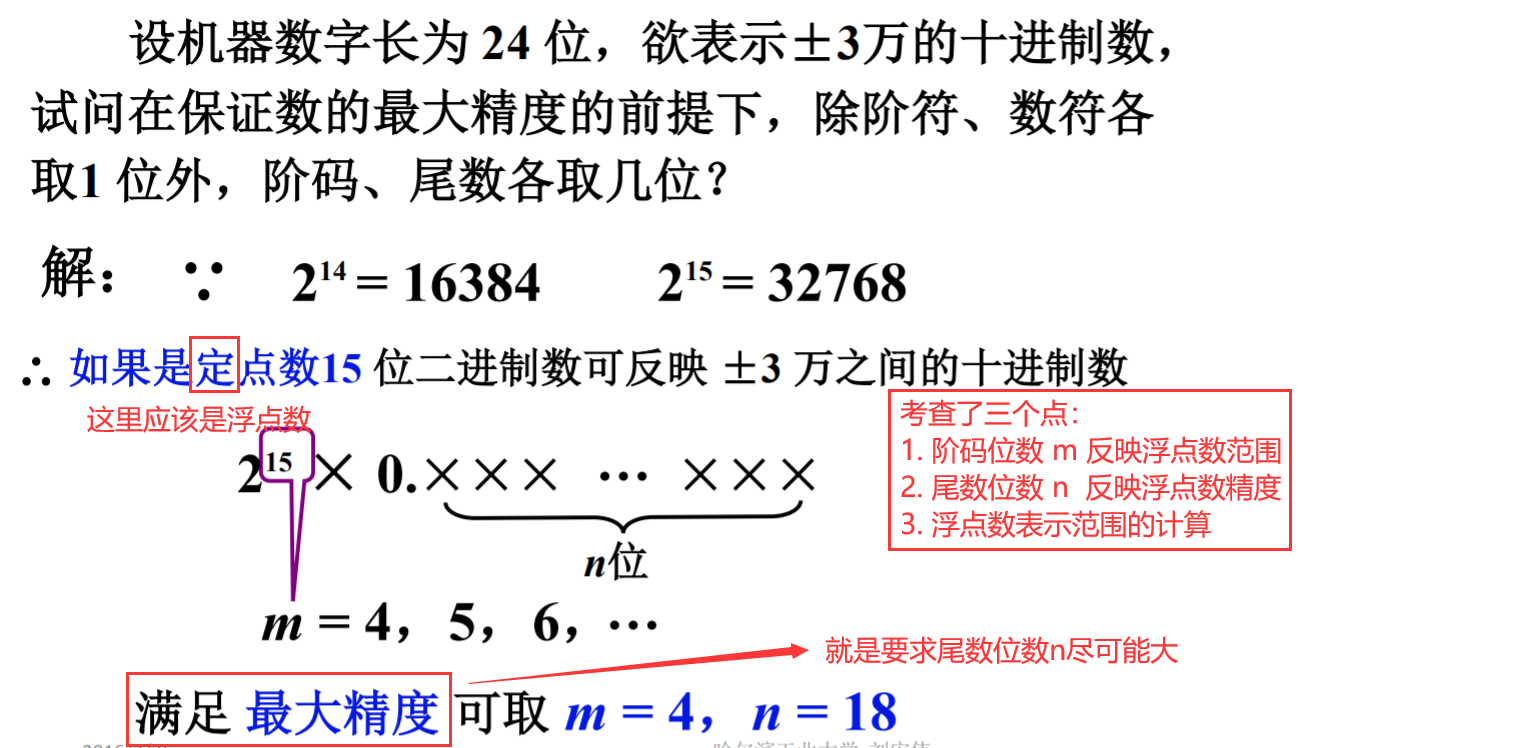

练习题:忽略图中 这里应该是浮点数

3. 浮点数的规格化形式

| 基数r取值 | 规格化形式 |

|---|---|

| 2 | 尾数最高位为1 |

| 4 | 尾数最高 2 位不全为 0(2 个二进制位表示 1 个四进制位) |

| 8 | 尾数最高 3 位不全为 0 (3 个 二进制位表示 1 个四进制位) |

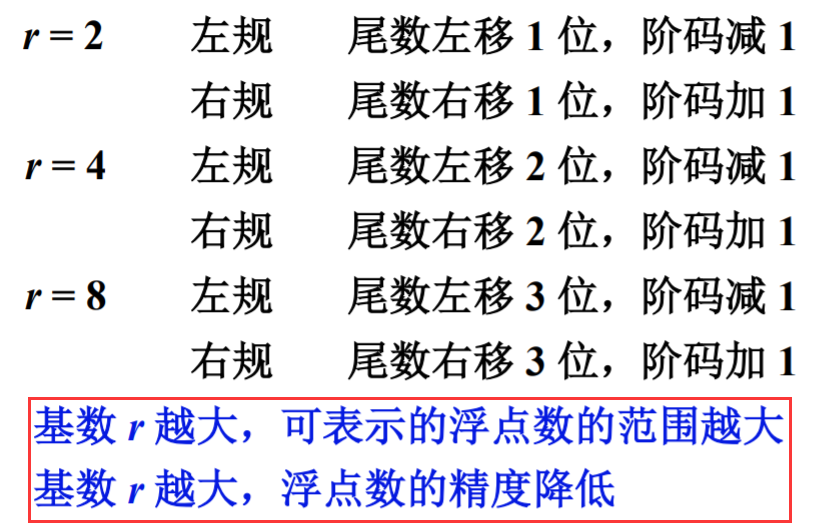

4. 浮点数的规格化

浮点数规格化的步骤:

- 尾数左移或后移,使尾数的最高几位满足规格化形式的要求

- 尾数左移:左规(数据相对小数点向左移动)

- 尾数右移:右规(数据相对小数点向右移动)

- 对阶码进行加减处理,使浮点数的真值不发生变化

需要注意到:规格化后浮点数的范围和未规格化浮点数的范围是不同的

3. 例题部分

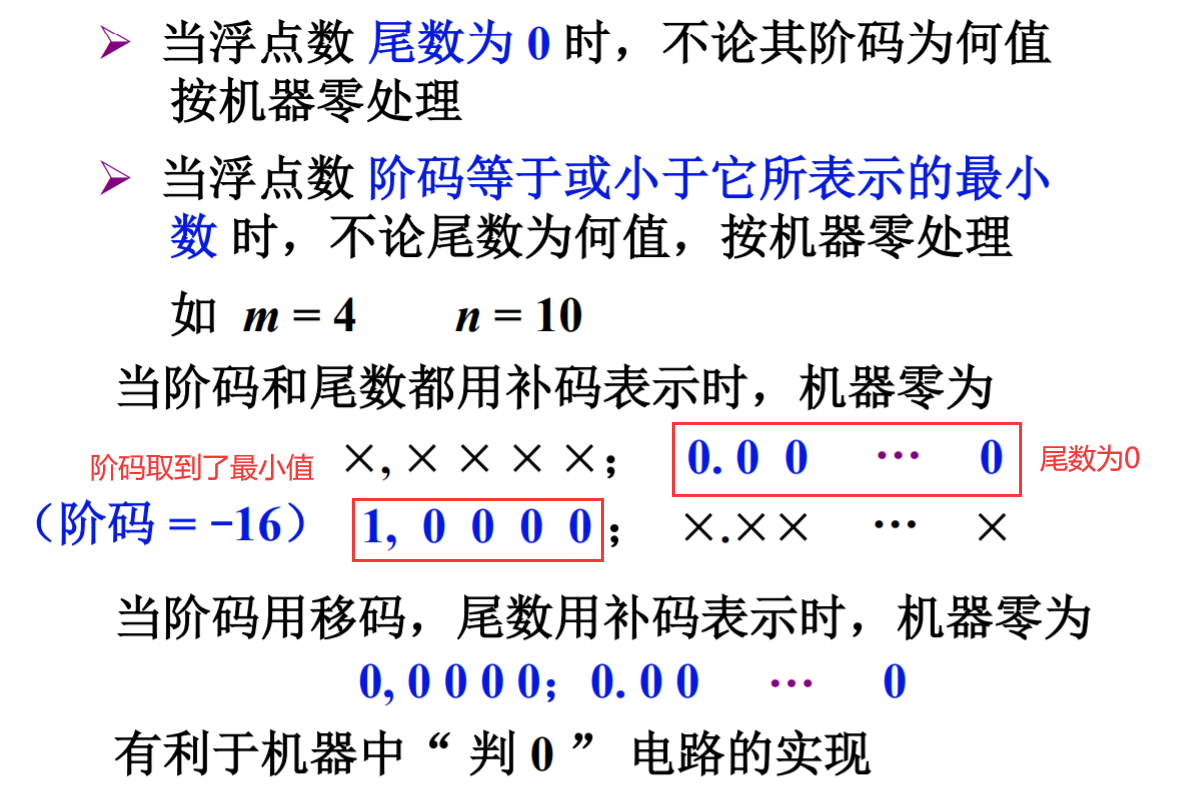

机器零

4. IEEE 754 标准

该标准同时要求:尾数必须采用规格化表示。特点如下:

- 尾数最高位必为1

- 只有一个小数点位置,它就是阶码的小数点位置,同时也是尾数的小数点位置

- 阶码为整数、尾数为纯小数

| 数值类型 | 符号位 S S S | 阶码 | 尾数 | 总位数 | |

|---|---|---|---|---|---|

| 短实数 | 1 | 8 | 23 | 32 | |

| 长实数 | 1 | 11 | 52 | 64 | |

| 临时实数 | 1 | 15 | 64 | 80 |

三、定点运算

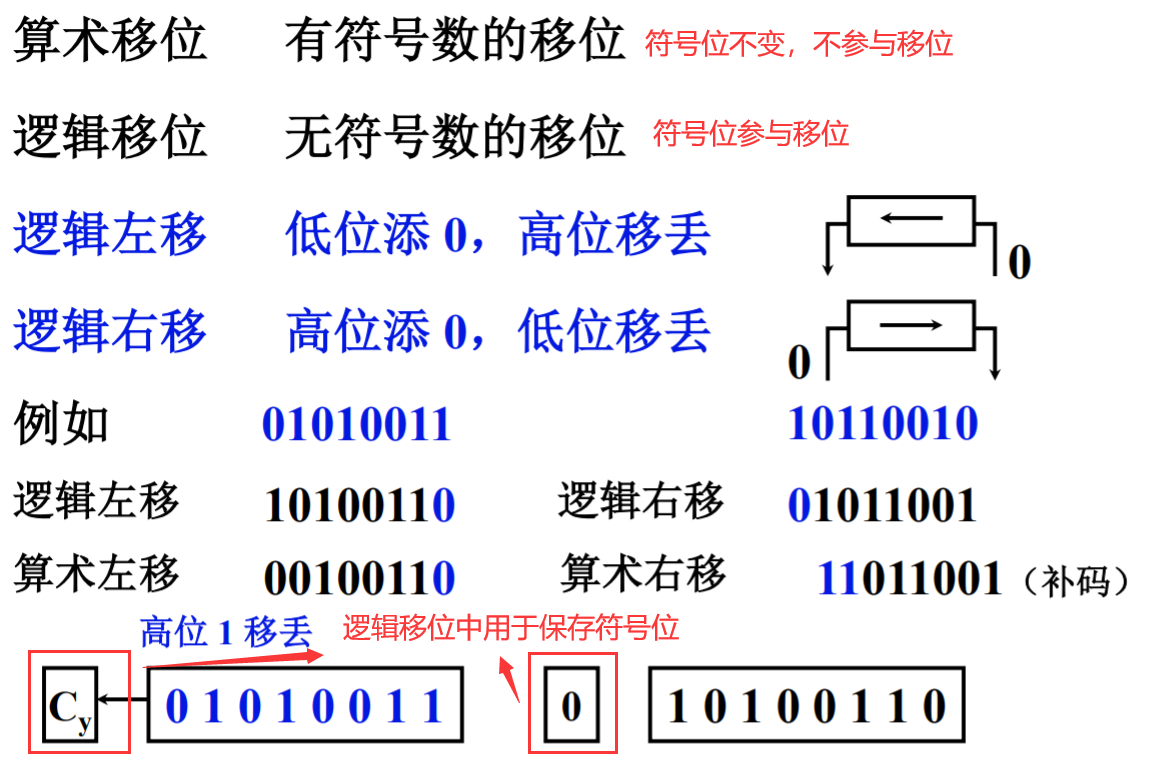

1. 移位运算

1. 移位的意义

如: 15. m = 1500. c m 15.\,m=1500.cm 15.m=1500.cm,相当于小数点右移两位。由于在计算机中小数点是按约定位置的,因此实际上小数点是不移动的。这种情况,我们称为:15 相对小数点左移两位(机器用语)

- 左移:绝对值扩大

- 右移:绝对值缩小

在计算机中,移位与加减配合,能够实现乘除运算

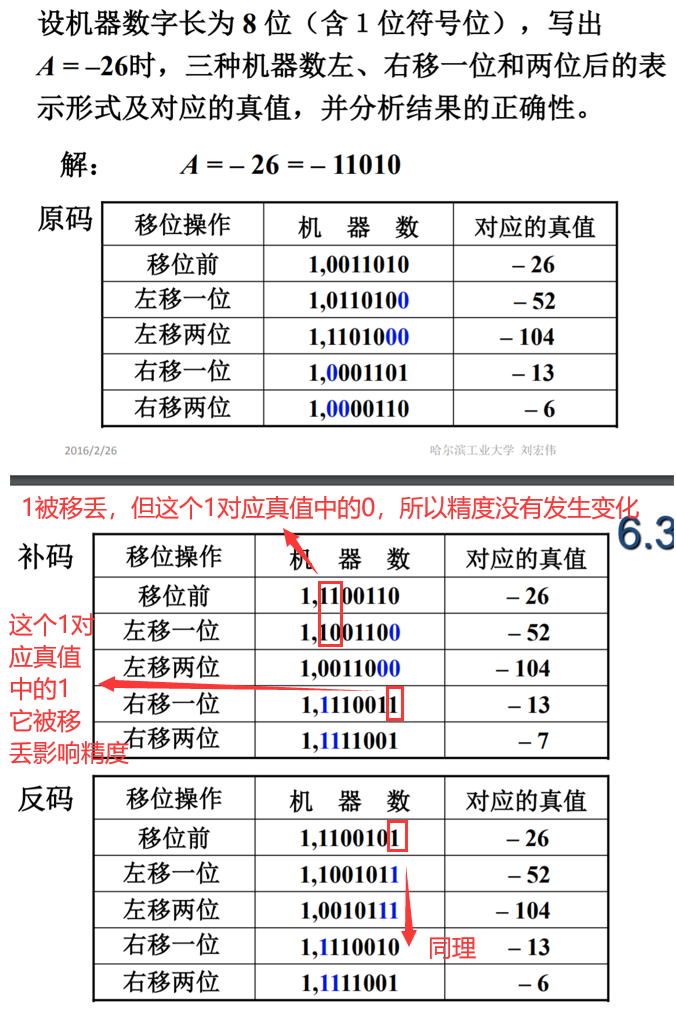

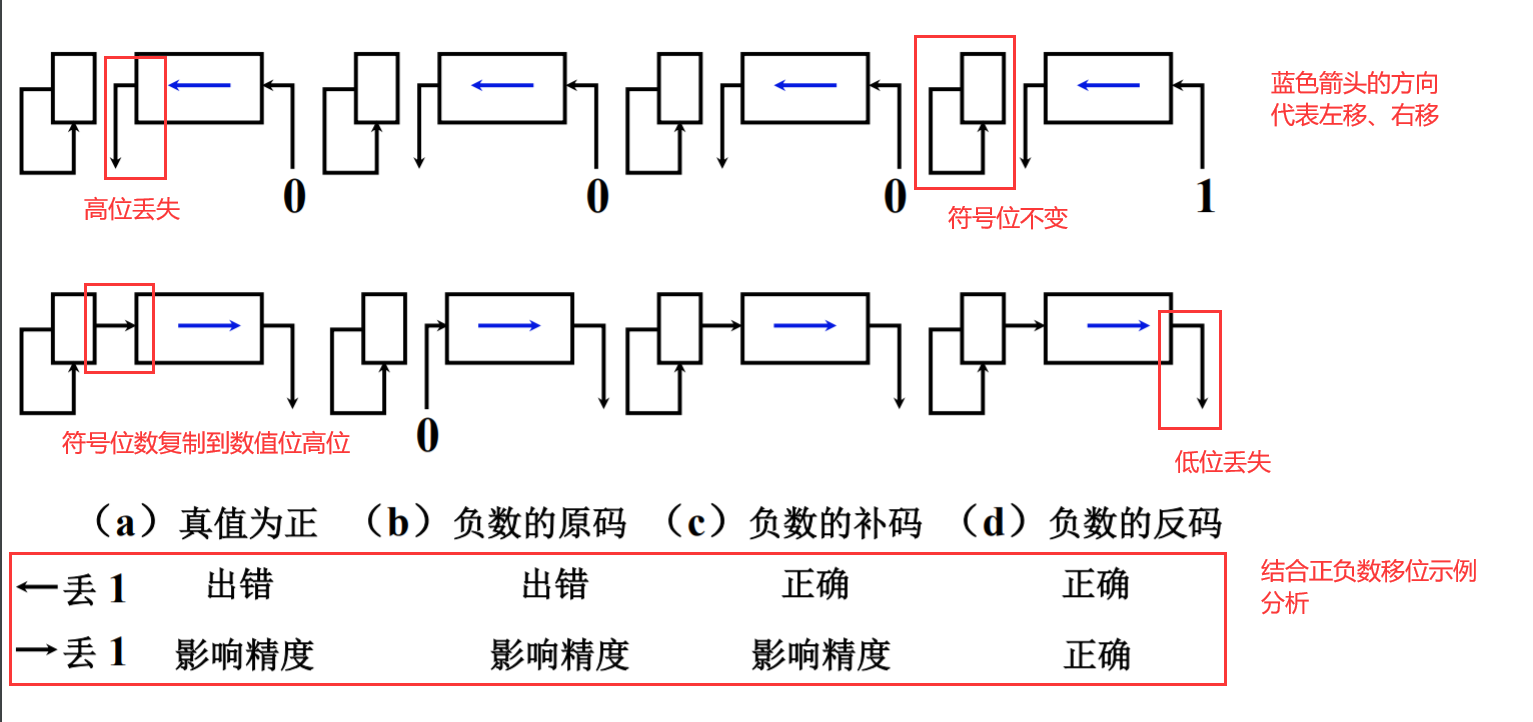

2. 算术移位规则

移位前提规则:符号位不变。移位添补规则如下:

1. 移位添补规则分析

2. 移位运算示例

1. 正数移位运算

结论:对于正数的移位运算,无论是原码、补码还是反码

- 左移:相当于 真 值 × 2 真值 \times 2 真值×2

- 右移:相当于 真 值 ÷ 2 真值 \div 2 真值÷2

在接下来的负数移位运算例子中,请着重关注移位丢失对数的精度造成的影响

2. 负数移位运算

当精度丢失时,补码、反码对应的原码和真值移位对应的原码就有差别了。

同时,将本例中反码左移三位,会发现运算结果出错。原因在于反码左移3位时丢失了一个高位0,而这个高位0对应真值中的高位1。

3. 算术移位的硬件实现

4. 算术移位和逻辑移位的区别

2. 加减法运算

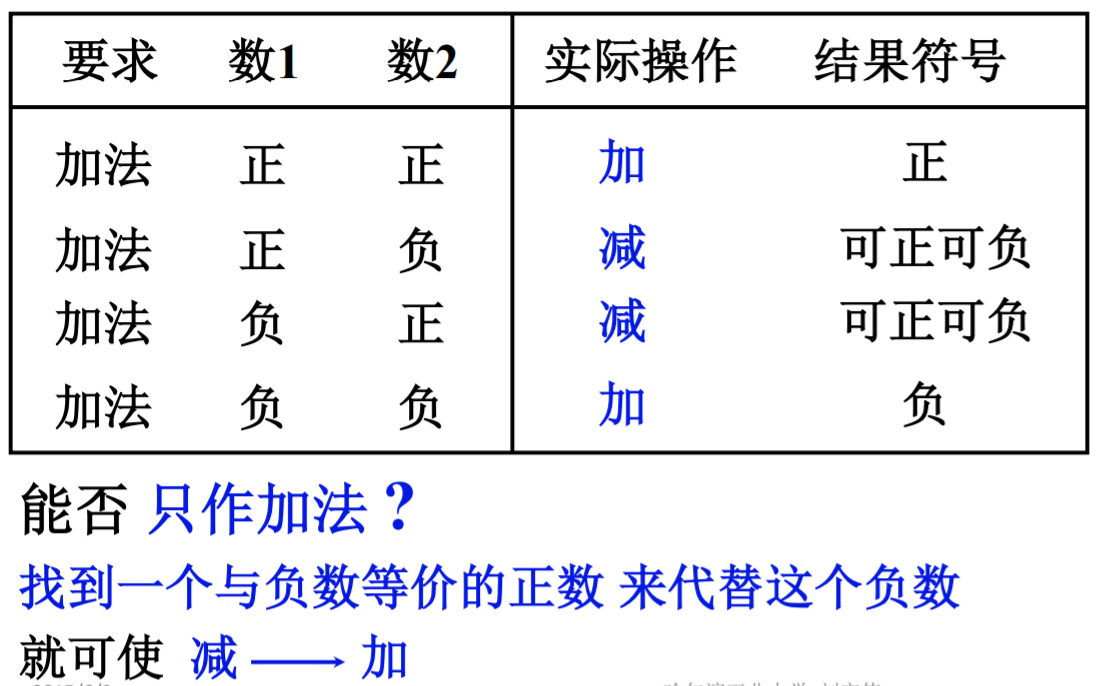

因为在前面的介绍中,我们知道使用原码进行加减法运算,需要根据数的符号判别到底是加法运算还是减法运算,实现复杂

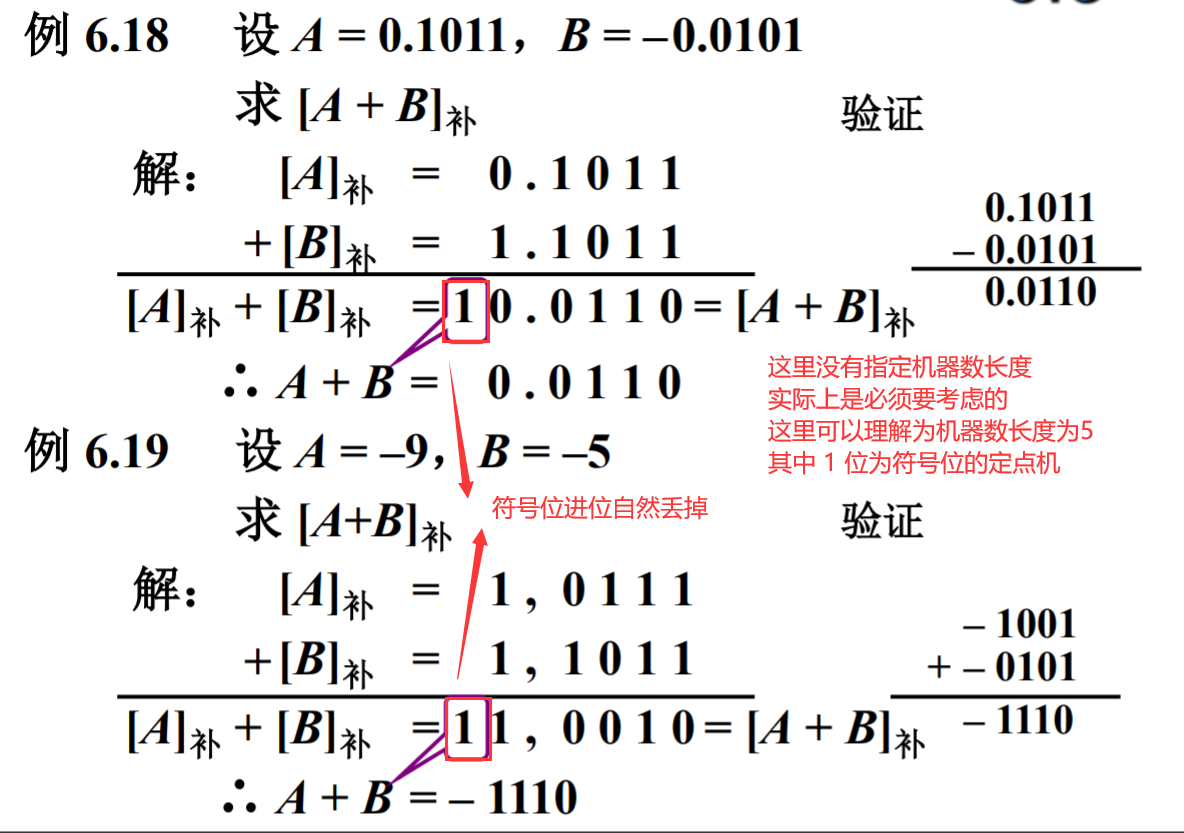

1. 补码加减法运算公式

整 数 [ A ] 补 + [ B ] 补 = [ A + B ] 补 ( m o d 2 n + 1 ) 小 数 [ A ] 补 + [ B ] 补 = [ A + B ] 补 ( m o d 2 ) 整数 \qquad [A]_补+[B]_补=[A+B]_补 \, (mod \, 2^{n+1})\\ 小数 \qquad [A]_补+[B]_补=[A+B]_补 \, (mod \, 2)\quad 整数[A]补+[B]补=[A+B]补(mod2n+1)小数[A]补+[B]补=[A+B]补(mod2)

整 数 [ A − B ] 补 = [ A + ( − B ) ] 补 = [ A ] 补 + [ − B ] 补 ( m o d 2 n + 1 ) 小 数 [ A − B ] 补 = [ A + ( − B ) ] 补 = [ A ] 补 + [ − B ] 补 ( m o d 2 ) 整数 \quad [A-B]_补=[A+(-B)]_补=[A]_补+[-B]_补 \, (mod\, 2^{n+1})\\ 小数 \quad [A-B]_补=[A+(-B)]_补=[A]_补+[-B]_补 \, (mod \, 2) 整数[A−B]补=[A+(−B)]补=[A]补+[−B]补(mod2n+1)小数[A−B]补=[A+(−B)]补=[A]补+[−B]补(mod2)

结论:在补码加减法运算中,实际上都是进行的加法。需要注意:

- 连同符号位一起相加,符号位产生的进位自然丢掉

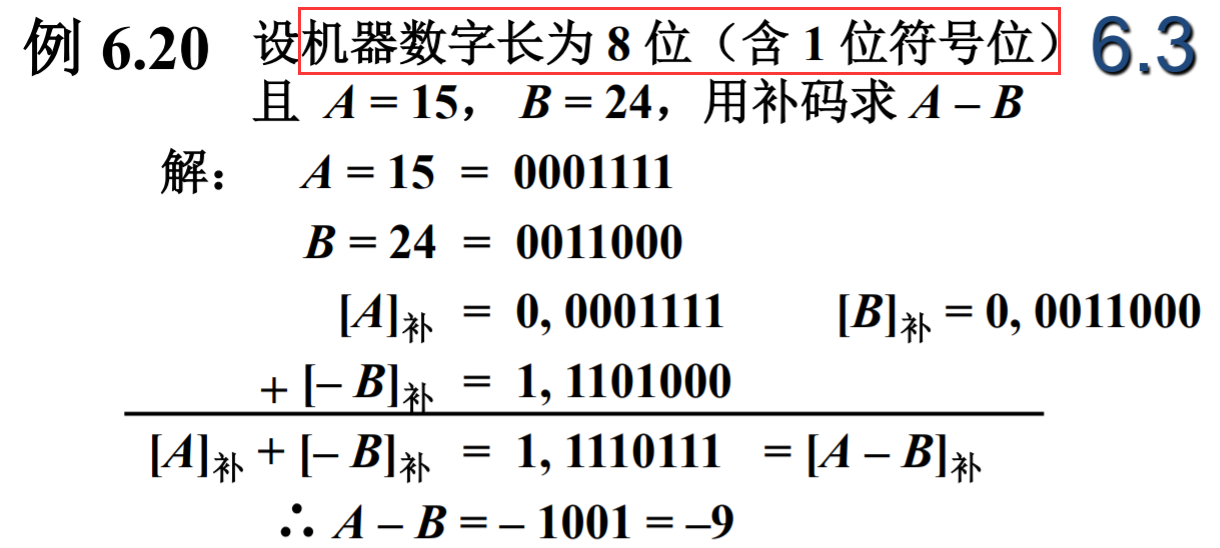

2. 两个例子

3. 溢出判断

- 练习一出错原因:纯小数定点机,运算结果>1,发生溢出

- 练习二出错原因:8位整数定点机,表示范围在 -128 ~ +127,运算结果超出了这个范围,产生溢出

溢出的概念:数据长度超出机器字长。(也可以说是,数据超过了机器所能表示数字的范围)

1. 一位符号位判溢出

判别方法:参与操作的两个数符号相同,其结果的符号与原操作数的符号不同,即为溢出。

分三种情况进行分析这个方法的正确性:

- 两个数异符号:即符号为一正一负,既然这两个数能够在定点机中表示,它们本身是不会溢出的,那么经过运算,结果肯定也不会溢出。

- 同为正数:假如运算结果变为负号,那就是发生了溢出。参考上面 练习一

- 同为负数:加入运算结果变为正号,那就是发生了溢出。参考上面 练习二(练习二可以看成是两个负数相加)

实现原理:

最

高

有

效

位

的

进

位

⨁

符

号

位

的

进

位

=

1

⟹

溢

出

最高有效位的进位 \bigoplus 符号位的进位 = 1 \quad \Longrightarrow 溢出

最高有效位的进位⨁符号位的进位=1⟹溢出。如:

有

溢

出

{

1

⨁

0

=

1

0

⨁

1

=

1

无

溢

出

{

0

⨁

0

=

0

1

⨁

1

=

0

有溢出\begin{cases} 1\bigoplus0=1 \\ 0\bigoplus1=1 \end{cases} \\ 无溢出 \begin{cases} 0\bigoplus0=0 \\ 1\bigoplus1=0 \end{cases}

有溢出{1⨁0=10⨁1=1无溢出{0⨁0=01⨁1=0

分析举例:

- 两个正数加法运算:假如两个正数均为 0,1xxxx ,那么经过运算后,最高有效位进位 1,符号位进位 0(即符号位没有进位),那么符号位就由 0 变 1,结果是负数。错误

- 两个负数加法运算:假如两个负数均为 1,0xxxx ,那么经过运算后,最高有效位进位 0,符号位进位 1,那么符号位就由 1 变 0,结果是正数。错误

2. 两位符号位判溢出

首先需要明确:两位符号位 代表 以4为模

补 码 计 算 公 式 : [ x ] 补 = { x 1 > x ≥ 0 4 + x 0 > x ≥ − 1 [ x ] 补 + [ y ] 补 = [ x + y ] 补 ( m o d 4 ) [ x − y ] 补 = [ x ] 补 + [ − y ] 补 ( m o d 4 ) 补码计算公式:[x]_补=\begin{cases} x \qquad 1>x\geq0 \\ 4+x\: 0>x\geq-1 \end{cases} \\ [x]_补+[y]_补=[x+y]_补(mod\,4)\\ [x-y]_补=[x]_补+[-y]_补(mod\,4) 补码计算公式:[x]补={x1>x≥04+x0>x≥−1[x]补+[y]补=[x+y]补(mod4)[x−y]补=[x]补+[−y]补(mod4)

判别原理:

4. 补码加减法的硬件配置

3. 乘法运算

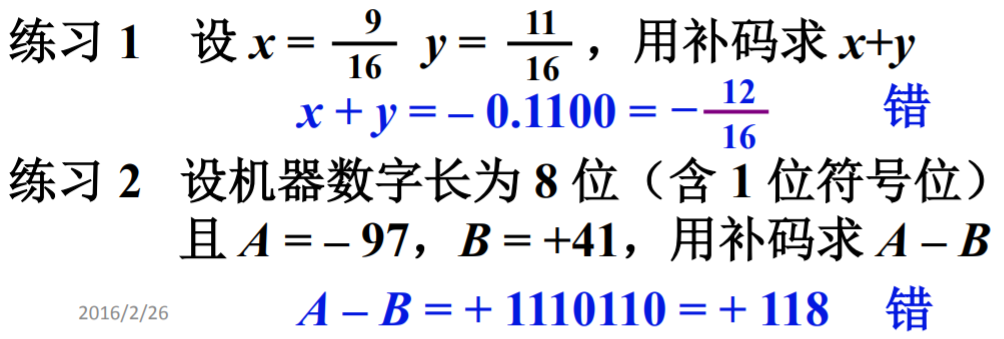

1. 分析笔算乘法

- 符号位单独处理:采用一个异或电路对符号进行处理

- 乘数的某一位决定是否加被乘数:将乘数放在移位寄存器中,每判断一次最低位,乘数右移一位(最低位丢失)

- 4个位积一起相加:用一个寄存器进行累加操作

- 乘积的位数扩大一倍:用两个寄存器一起保存乘积

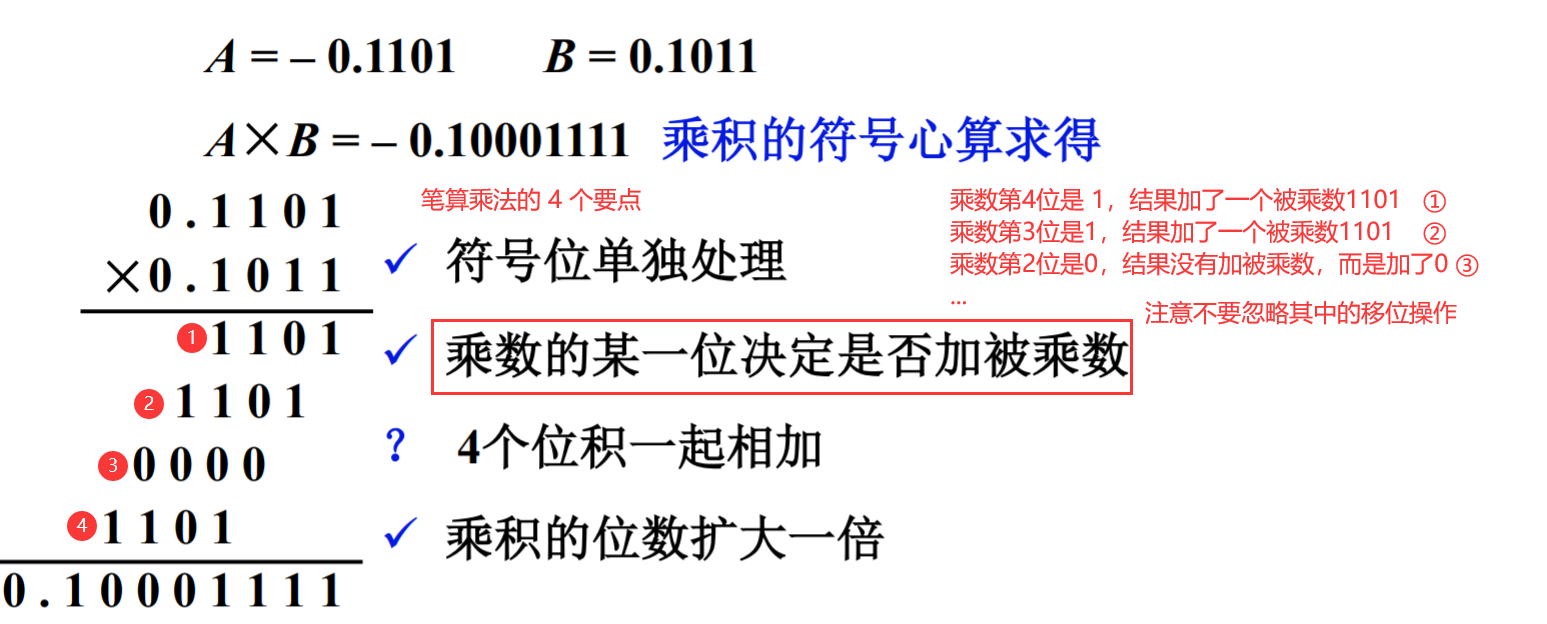

2. 笔算乘法改进

3. 改进后的笔算乘法过程(竖式)

- 部分积初始值为 0

- 根据乘数末位的值判断部分积加值,结果记为 X

- 乘数末位为1,部分积 + 被乘数

- 乘数末位为0,部分积 + 0

- 将 2. 的结果X右移一位,形成新的部分积

- 乘数右移一位,末位移丢(因为末位判断过了,要判断倒数第二位的值了)。

- 从 2. 开始循环,直到乘数全部判断完成

注意:

- 每一轮循环执行了两次移位,X移位一次,乘数移位一次

- X移位时丢出来的低位数据,放在了乘数移位空出来的高位位置

- 这里用到了3个寄存器,有2个分别保存部分积高位和乘数(和部分积低位),具有移位功能。1个用于保存被乘数,不具有移位功能

- 当计算完成后,两个寄存器合起来才是结果。其中:

- 部分积寄存器保存结果的高位部分

- 乘数寄存器保存结果的低位部分

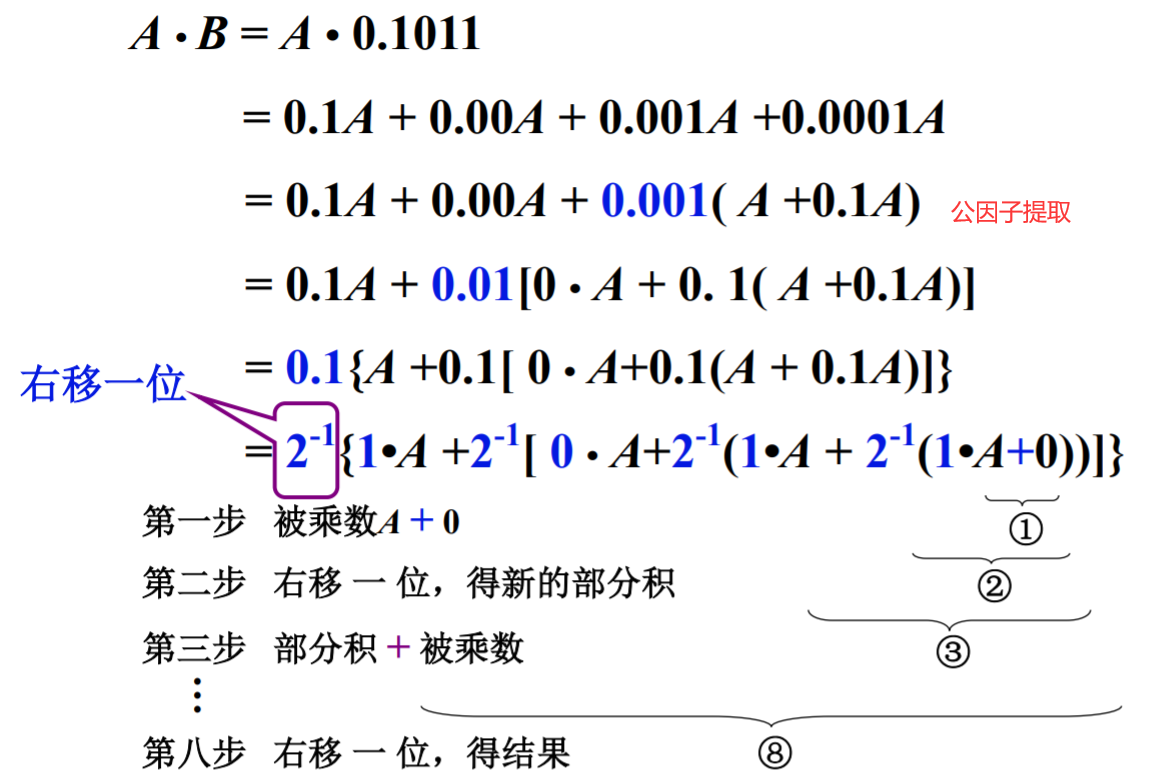

4. 小结

- 乘法 运算可用 加和移位实现。n位数据的乘法运算,需要n次加法运算和n次移位运算。n指运算数数据部分长度

- 由乘数的末位决定被乘数是否与原部分积相加, 然后 右移1位 形成新的部分积,同时 乘数 右移1 位 (末位移丢),空出高位存放部分积的低位。

- 被乘数只与部分积的高位相加

- 硬件:3个寄存器(其中两个有移位功能),1个全加器(n+1位,实现相加操作)

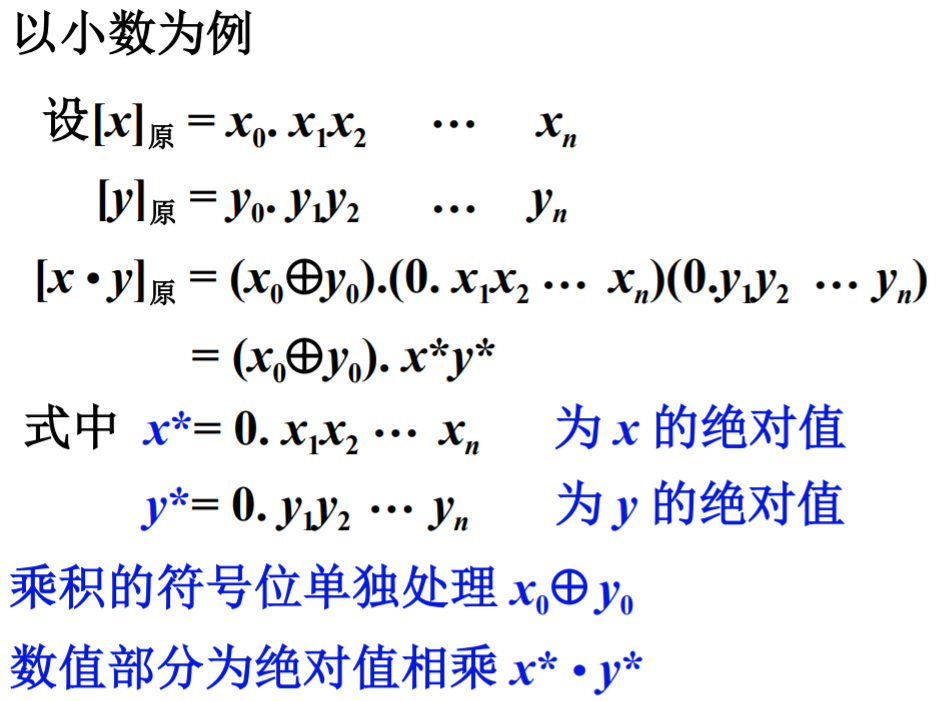

5. 原码乘法

1. 原码一位乘运算规则

2. 原码一位乘递推公式

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-xYAZyPYE-1651754934531)(https://i.loli.net/2021/11/17/iLFTlahbf5njwpy.png)]

特点:

- 绝对值运算

- 用移位的次数判断乘法是否结束

- 逻辑移位

3. 原码一位乘的硬件配置

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JmG725Ld-1651754934532)(https://i.loli.net/2021/11/17/mgosj1BTkC5fLNV.png)]

- A、X、Q 均 n+1 位

- 移位和加受乘数末位控制

6. 补码乘法

4. 除法运算

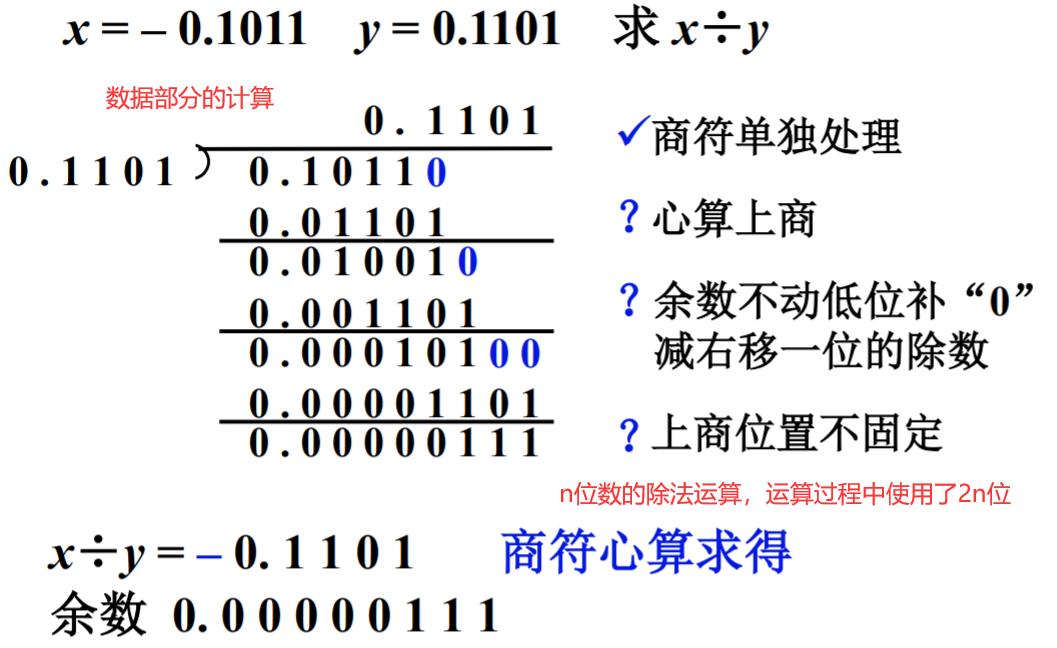

1. 分析笔算除法

2. 笔算除法和机器除法的比较

需要注意的点:

- x 在第一次计算时,是被除数。从第二次开始,代表的就是余数了。而y始终代表除数。看恢复余数法中的例子

- 余数左移一位 和 除数右移一位 相对而言是等价的

- 使用1倍字长加法器原因:用余数左移一位代替除数右移一位后,不会产生更多的位数

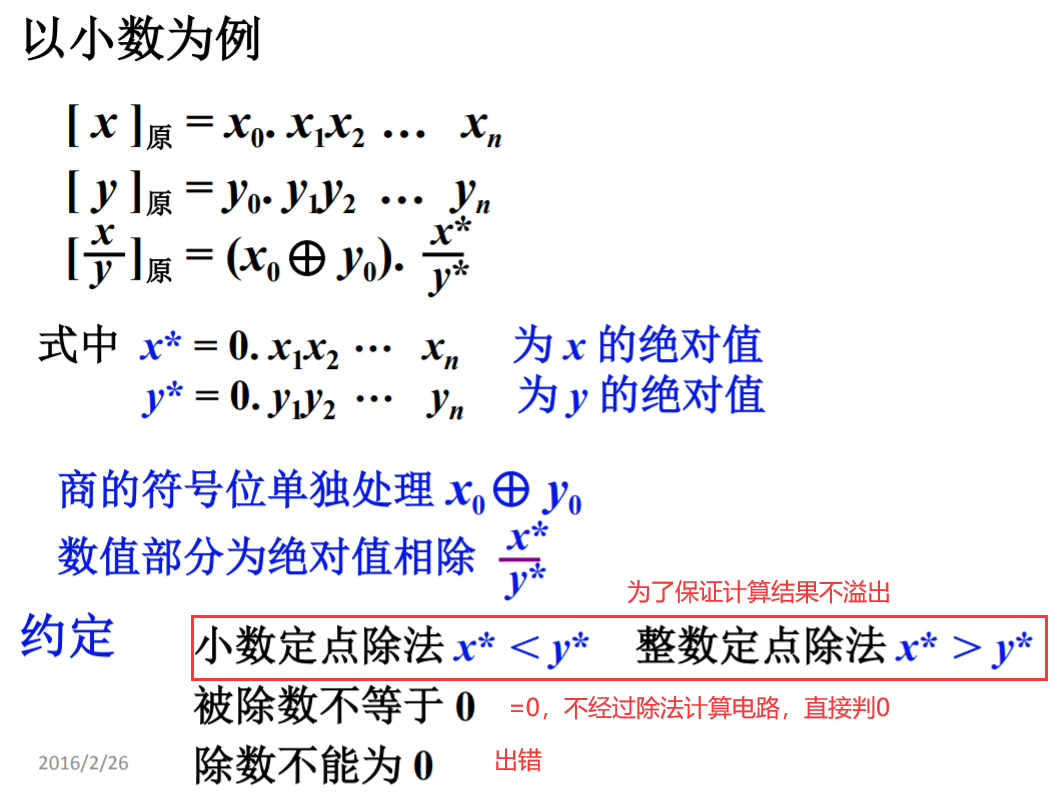

3. 原码除法

计算机中除法运算的实现有两种:恢复余数法、不恢复余数法(加减交替法)。

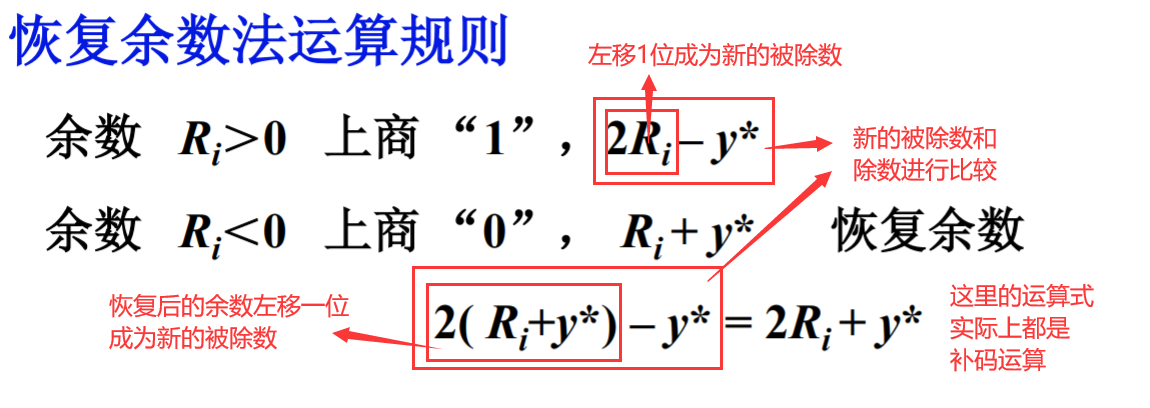

1. 恢复余数法

假如求 [ x y ] 原 [\frac{x}{y}]_原 [yx]原,算法步骤:

- 被除数和除数进行比较,判断商值。计算机通过补码减法运算判断:

[

x

∗

]

补

−

[

y

∗

]

补

=

[

x

∗

]

补

+

[

−

y

∗

]

补

x

∗

,

y

∗

代

表

绝

对

值

[x^*]_补-[y*]_补=[x^*]_补+[-y*]_补 \qquad x^*,y^*代表绝对值

[x∗]补−[y∗]补=[x∗]补+[−y∗]补x∗,y∗代表绝对值

- 余数为正数,上商为1,余数为x (x的值变了)

- 余数为负数,上商为0 同时恢复被除数 x(上商为1代表这步减法是合规的,上商为0代表这里不能做减法,因此要恢复)

- 注意: [ x ∗ ] 原 = [ x ∗ ] 补 = [ x ∗ ] 反 [x^*]_原=[x^*]_补=[x^*]_反 [x∗]原=[x∗]补=[x∗]反。

- x 逻辑左移1位成为新的被除数。从第1步开始循环

特点:

- x 代表的值一直在变化(做减法、做移位),而 y 代表的值是不发生变化的

- x 从第二步开始就代表了余数(左移1位后成为新一轮除法运算的被除数),因为x可能会被恢复,因此这种方法名为 恢复余数法

- 每一轮循环都会移位一次。n位的被除数,共移位n次

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cZCuW8No-1651754934535)(https://i.loli.net/2021/11/17/dx7uUTPZeKM3wAY.png)]

特点:

- 上商 n+1 次

- 第一次上商判溢出

- 移位 n 次,加法 n+1 次

- 用移位的次数判断除法是否结束

在纯小数定点机中,假如第一次上商为1,代表结果>1,产生了溢出。

恢复余数法运算规则:

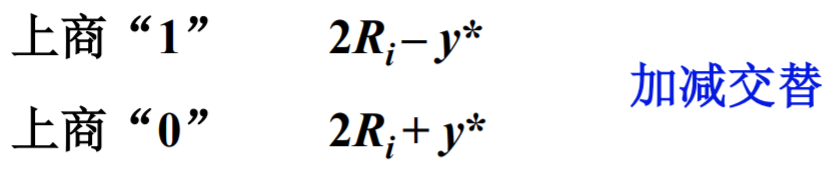

2. 不恢复余数法(加减交替法)

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-lLzZ36sE-1651754934538)(D:/%E5%A4%A7%E5%AD%A6%E8%B5%84%E6%96%99/%E8%AE%A1%E7%AE%97%E6%9C%BA%E7%BB%84%E6%88%90%E5%8E%9F%E7%90%86/img/%E4%B8%8D%E6%81%A2%E5%A4%8D%E4%BD%99%E6%95%B0%E6%B3%95%E4%BE%8B%E5%AD%90.png)]

特点:

- 上商 n+1 次

- 第一次上商判溢出

- 移n次,加 n+1 次

- 用移位的次数判断除法是否结束

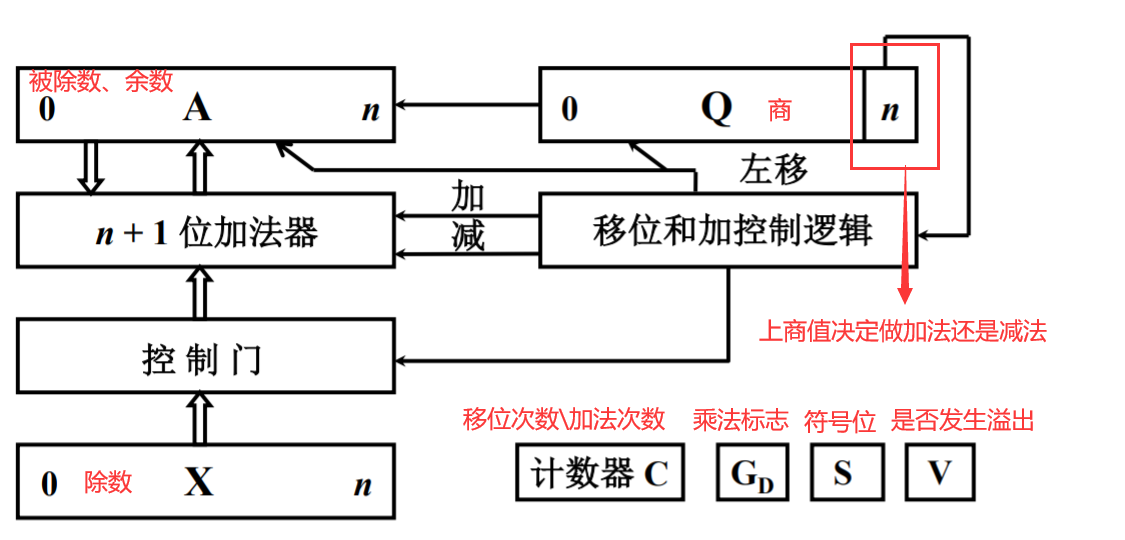

3. 原码加减交替除法硬件配置

四、浮点四则运算

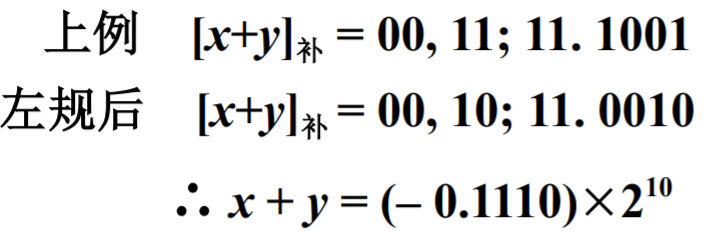

1. 浮点加减法运算

1. 对阶

浮点数运算有两个前提要求:

- 基值相同

- 阶码相同

只有满足这两个要求,才能保证尾数进行加减法运算结果的正确性。而在基值相同的情况下,调整阶码使阶码相同就是对阶。对阶时尾数也要调整(保证真值不变)

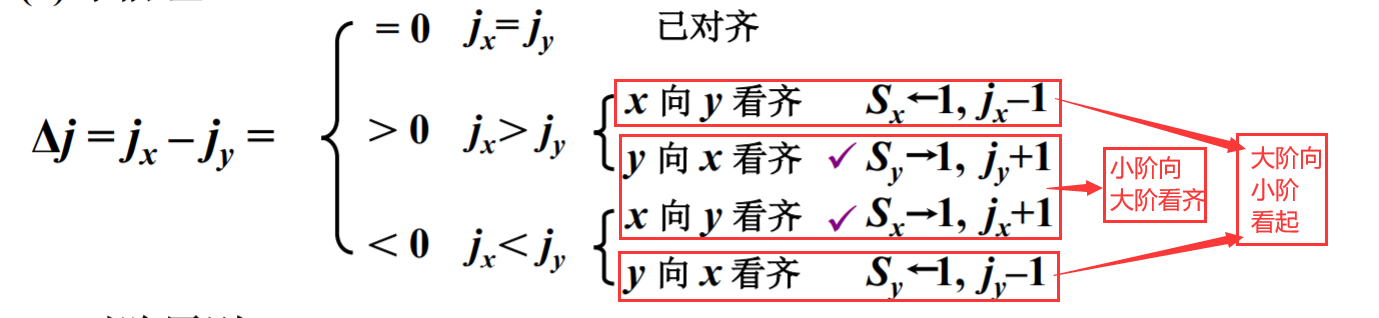

1. 求阶差

计算机中,通过对阶码进行补码减法运算,判断阶差,并对阶码进行调整。下图给出了阶差公式及所有的调整方案:

2. 对阶原则

计算机采用的对阶原则是:小阶向大阶看起。原因:高位丢失影响大小,低位丢失影响精度。高位丢失和低位丢失对比

3. 规格化

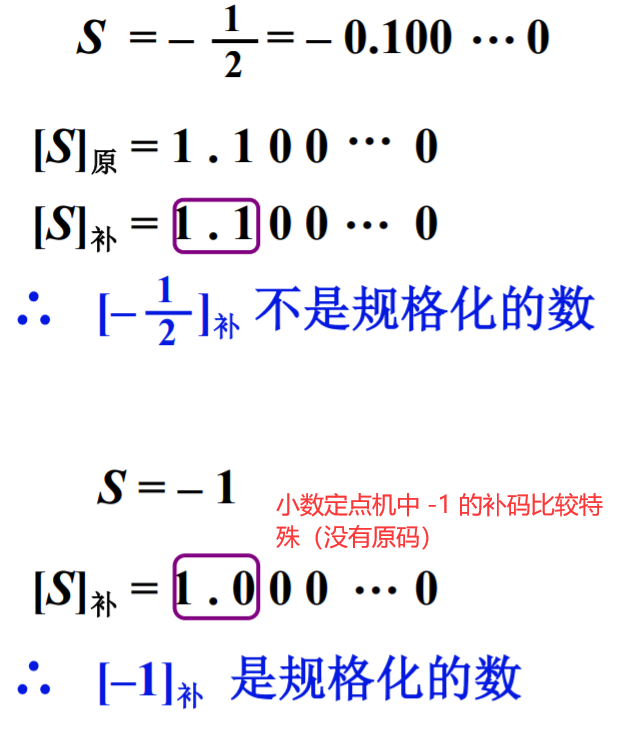

1. 规格化数的定义

如下:

通

用

定

义

:

1

r

≤

∣

S

∣

<

1

r

代

表

基

值

当

r

=

2

时

:

1

2

≤

∣

S

∣

<

1

通用定义:\frac{1}{r}\leq|S|<1 \qquad r代表基值 \\ 当\,r=2\,时:\frac{1}{2}\leq|S|<1 \qquad

通用定义:r1≤∣S∣<1r代表基值当r=2时:21≤∣S∣<1

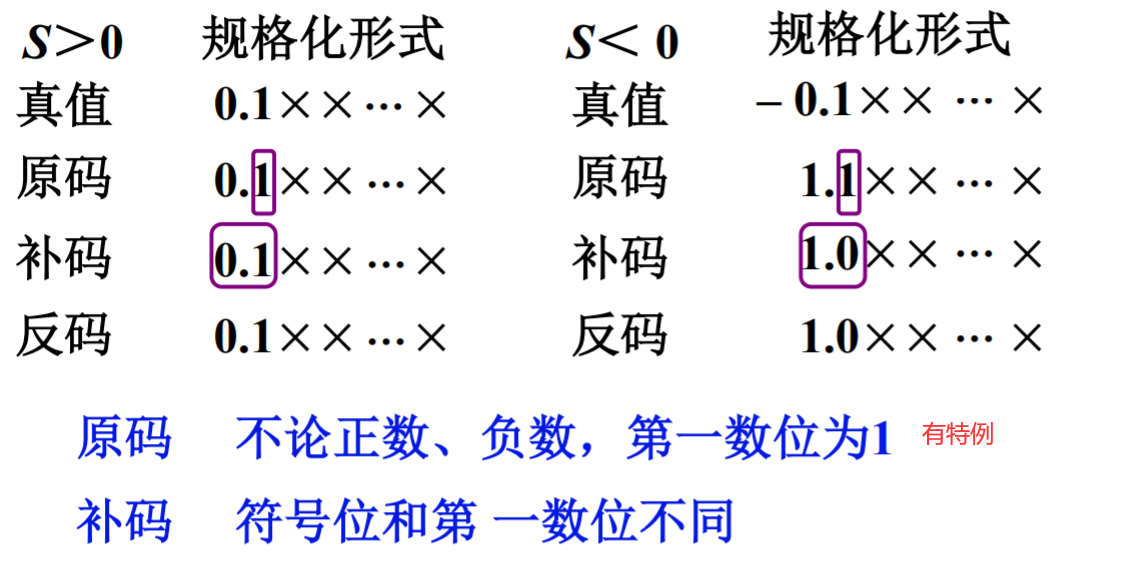

2. 规格化数的判断

3. 左规

机器数采用补码:尾数左移一位(算数移位),阶码减 1,直到数符和第一数位不同为止。对阶例题

4. 右规

使用条件:当 尾数溢出( >1)时,需 右规。即尾数出现 01. ×× …×或 10. ×× …×时

机器数采用补码:尾数右移一位(算术移位),阶码加 1

4. 舍入

在 对阶 和 右规 过程中,可能出现 尾数末位丢失 引起误差,需考虑舍入。两种舍入方案:

- 0舍1入法:

- 末位丢失0:不做处理

- 末位丢失1:末位+1

- 恒置1法:无论末位丢失0或1,始终把末位设为1

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-40c2bwW7-1651754934542)(https://i.loli.net/2021/11/18/L5hM2T1nfNovudi.png)]

5. 溢出判断

最值的计算方法参考 [浮点数的范围计算](#2. 浮点数的表示范围)

五、算数逻辑单元

1. ALU电路

2. 快速进位链

1. 并行加法器

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-b6vBbWCt-1651754934543)(https://i.loli.net/2021/11/18/yJdpaDTR2o5kPv7.png)]

整体来看:

-

A

0

⋯

A

n

A_0 \cdots A_n

A0⋯An,输入

x

x

x的值。

B

0

⋯

B

n

B_0 \cdots B_n

B0⋯Bn,输入

y

y

y的值。

- A i A_i Ai 对应 x x x 中的 第 i i i 位(自👉至👈)

- B i B_i Bi 对应 y y y 中的 第 i i i 位(自👉至👈)

- 因此, F A i FA_i FAi 实际上执行的是两个运算数中 同一位置的进制位的 加法运算

取单个模块来看,如图中的 F A 0 FA_0 FA0:

- A 0 、 B 0 A_0、B_0 A0、B0分别输入 x 的 最 低 位 、 y 的 最 低 位 x的最低位、y的最低位 x的最低位、y的最低位

- C − 1 C_{-1} C−1 代表低一位的计算进位

- A 0 、 B 0 、 C − 1 A_0、B_0、C_{-1} A0、B0、C−1进行计算,结果中低位保存在 S 0 S_0 S0,高位经 C 0 C_0 C0 传递给下一高位的计算单元 F A 1 FA_1 FA1(运算结果可能是2位或1位)

分析本位结果 S i S_i Si 取1的情况和 进位结果 C i C_i Ci 取1的情况:

-

S

i

=

1

S_i=1

Si=1:

- A i 、 B i 、 C i − 1 A_i、B_i、C_{i-1} Ai、Bi、Ci−1,三者中任意一个为1,剩余两个为0

- A i 、 B i 、 C i − 1 A_i、B_i、C_{i-1} Ai、Bi、Ci−1,三者都为1

-

C

i

=

1

C_i=1

Ci=1:

- A i 、 B i 、 C i − 1 A_i、B_i、C_{i-1} Ai、Bi、Ci−1,三者中任意两个为1,剩余一个为0

- A i 、 B i 、 C i − 1 A_i、B_i、C_{i-1} Ai、Bi、Ci−1,三者都为1

S i = A i ‾ B i ‾ C i − 1 + A i ‾ B i C i − 1 ‾ + A i B i ‾ C i − 1 ‾ + A i B i C i − 1 C i = A i ‾ B i C i + A i B i ‾ C i + A i B i C i − 1 ‾ + A i B i C i − 1 = A i B i + ( A i + B i ) C i − 1 = d i + t i C i − 1 其 中 : d i = A i B i ( 本 地 进 位 ) t i = A i + B i ( 传 送 条 件 ) S_i= \overline{A_i}\,\overline{B_i}\,C_{i-1} + \overline{A_i}\,B_i\,\overline{C_{i-1}} + A_i\,\overline{B_i}\ \overline{C_{i-1}} + A_i\,B_i\,C_{i-1} \\ \begin{aligned} C_i &= \overline{A_i}\,B_i\,C_i + A_i\,\overline{B_i}\,C_i + A_i\,B_i\,\overline{C_{i-1}} + A_i\,B_i\,C_{i-1} \\ &= A_iB_i + (A_i+B_i)C_{i-1} \\ &= d_i + t_iC_{i-1} \end{aligned} \\ 其中:d_i=A_iB_i (本地进位) \qquad t_i=A_i+B_i (传送条件) Si=AiBiCi−1+AiBiCi−1+AiBi Ci−1+AiBiCi−1Ci=AiBiCi+AiBiCi+AiBiCi−1+AiBiCi−1=AiBi+(Ai+Bi)Ci−1=di+tiCi−1其中:di=AiBi(本地进位)ti=Ai+Bi(传送条件)

并行加法器的特点:

- 每一位的计算依赖于前一位的计算结果(低位的进位值),自👉至👈逐位计算,逐级传递进位

- 当 A i 、 B i A_i、B_i Ai、Bi只有一个是 1 时,有 C i = C i − 1 C_i=C_{i-1} Ci=Ci−1, C i C_i Ci的推论式可证明

注意:在公式中,记法可以理解为或运算,乘法可以理解为与运算

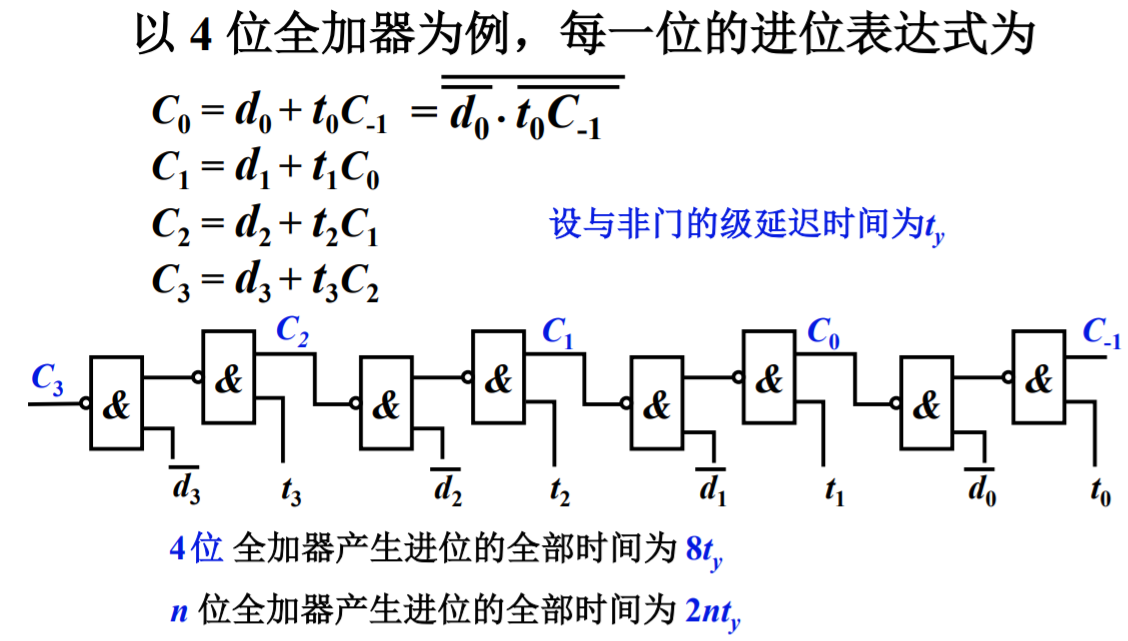

2. 串行进位链

- 进位链:传送进位的电路

- 串行进位链:进位信号采用串行传递

在对并行加法器的分析中我们得知:进位的传递速度会影响加法器的计算速度。因此,单独处理进位操作,设计实现快速进位,可以提高加法器的计算速度。这就是进位链的作用。

| A 0 , B 0 A_0,B_0 A0,B0 | C − 1 C_{-1} C−1 | d 0 d_0 d0 | d 0 ‾ \overline{d_0} d0 | t 0 t_0 t0 | t 0 & C − 1 t_0 \, \& \, C_{-1} t0&C−1 | C 0 = d 0 ‾ & ( t 0 & C − 1 ) C_0=\overline{d_0}\, \& \, (t_0 \, \& \, C_{-1}) C0=d0&(t0&C−1) | 输入值中1的个数 |

|---|---|---|---|---|---|---|---|

| 都是1 | 1 | 1 | 0 | 1 | 0 | 1 | 3 |

| 都是1 | 0 | 1 | 0 | 1 | 1 | 1 | 2 |

| 任一为1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 |

| 任一为1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 都是0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 都是0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

补充说明:

- t 0 & C − 1 t_0 \, \& \, C_{-1} t0&C−1:第一次 与非门 运算(异或运算)

- d 0 ‾ & ( t 0 & C − 1 ) \overline{d_0}\, \& \, (t_0 \, \& \, C_{-1}) d0&(t0&C−1):第二次 与非门 运算(异或运算),同时也是进位的结果

- d 0 = A 0 & & B 0 t 0 = A 0 ∣ ∣ B 0 d_0=A_0\, \&\& \,B_0 \qquad t_0=A_0\,||\,B_0 d0=A0&&B0t0=A0∣∣B0

C 0 = d 0 + t 0 C − 1 = d 0 ∣ ∣ ( t 0 & & C − 1 ) = 非 d 0 ‾ ∣ ∣ [ 非 ( t 0 ∣ ∣ c − 1 ) ] = 非 [ ( d 0 ‾ ) & & ( t 0 ∣ ∣ C 1 ] ( 德 摩 根 率 ) = 非 { d 0 ‾ & & [ 非 ( t 0 & & C − 1 ) ] } \begin{aligned} C_0 &= d_0+t_0 C_-1 \\ &= d_0\, || \,(t_0 \, \&\& \, C_{-1}) \\ &= 非\,\overline{d_0}\, || \,[\,非\,(t_0\, || \, c_{-1})\,] \\ &= 非\,[\,(\overline{d_0})\, \&\& \,(t_0\, || \,C_{_1}] \quad(德摩根率) \\ &= 非\, \{\, \overline{d_0}\, \&\&\,[\,非\, (\,t_0\, \&\&\, C_{-1})\,] \,\} \\ \end{aligned} C0=d0+t0C−1=d0∣∣(t0&&C−1)=非d0∣∣[非(t0∣∣c−1)]=非[(d0)&&(t0∣∣C1](德摩根率)=非{d0&&[非(t0&&C−1)]}

显然,串行进位链依然是采用逐级传递进位的方式

3. 并行进位链

- 根据上图中的算式推演,4个进位的产生只和 C − 1 C_{-1} C−1有关,一旦已知 C − 1 C_{-1} C−1值,4个进位同时产生。因为t和d的生成只与A、B有关

- 进位链电路中:

- 下层是一个与或非门,在推演的算式中:每一项内部是乘法(为与操作),各项结果执行或操作即可得出答案。因此与或非门多执行了一次非操作,所以与或非门的结果再执行一次非门才是正确结果

- 最高位

C

3

C_3

C3的进位产生电路和其他进位的产生电路是不同的。其执行逻辑为:

- 前四项执行与或非逻辑,最后一项执行与非逻辑。得出的两个结果都是正确结果取非后的结果

- 将这两项结果取非后进行或操作,即可得出正确进位

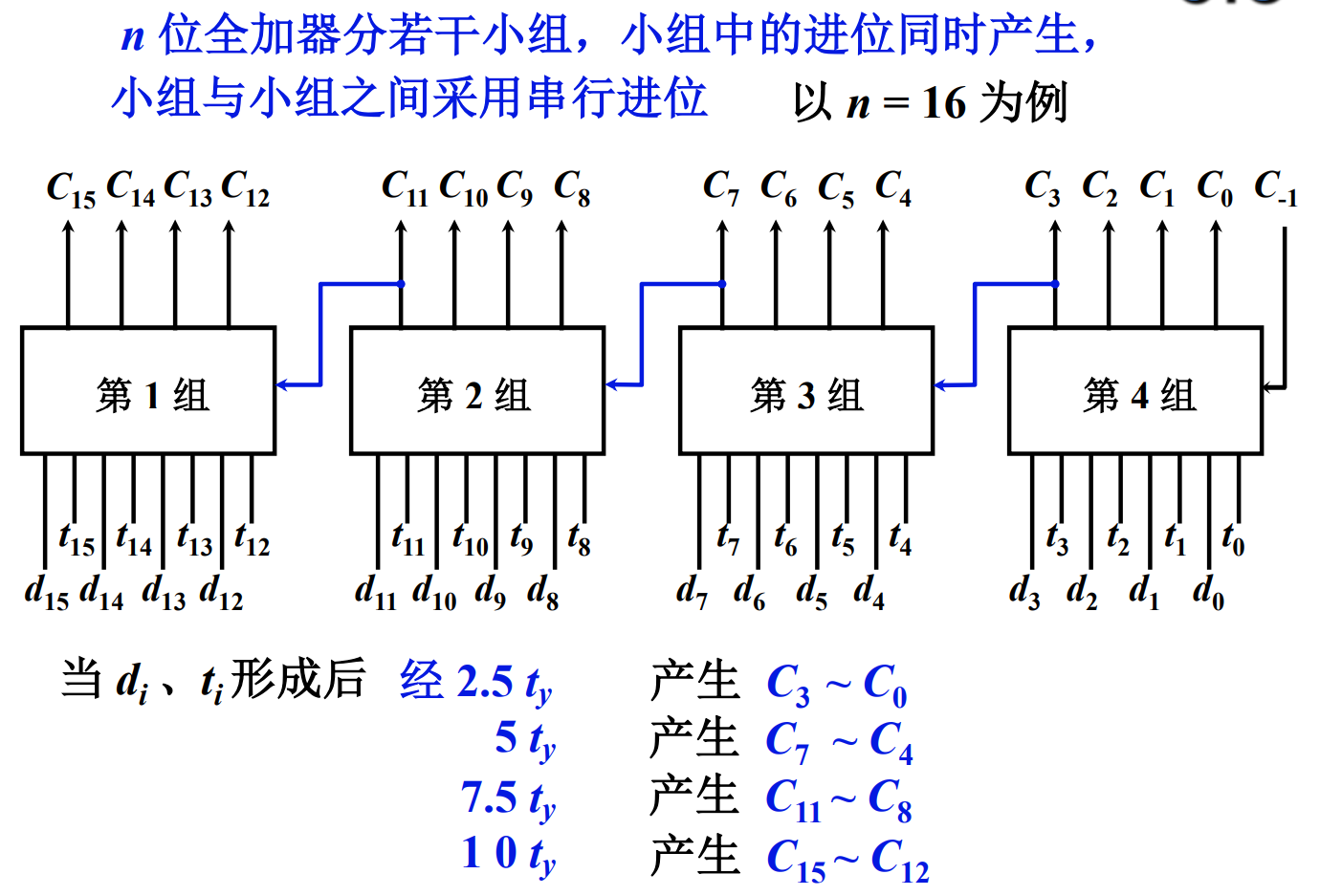

1. 单重分组跳跃进位链

- 小组内的进位产生和4位加法器进位链是一样的

- 每一小组组内进位是同时产生的。小组间采用串行进位意味着只有前一小组进位产生后,后一小组的进位才会产生,如

- 第4小组进位同时产生后,第3小组的进位才会同时产生

- 第3小组进位同时产生后,第2小组的进位才会同时产生

- …

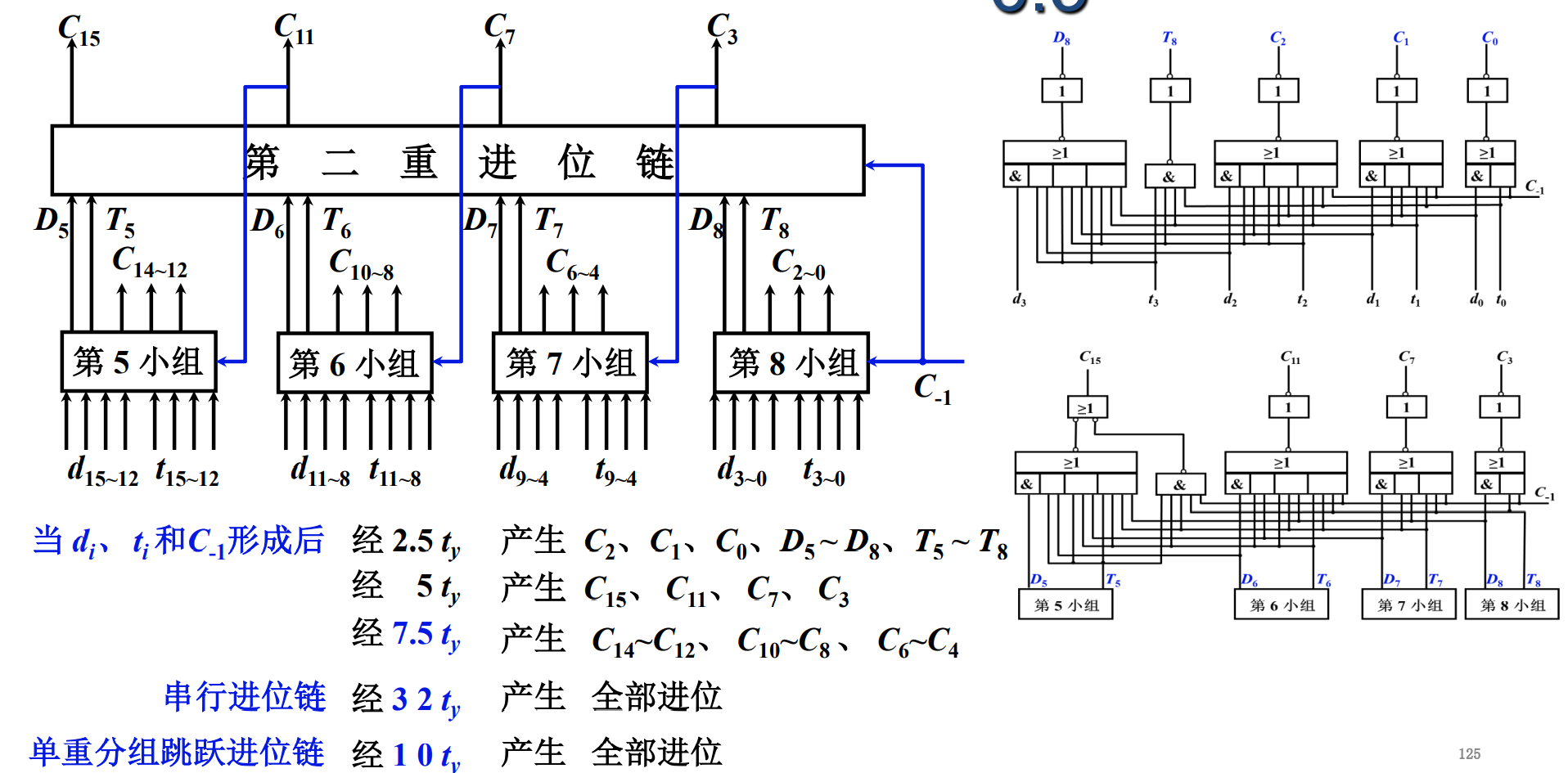

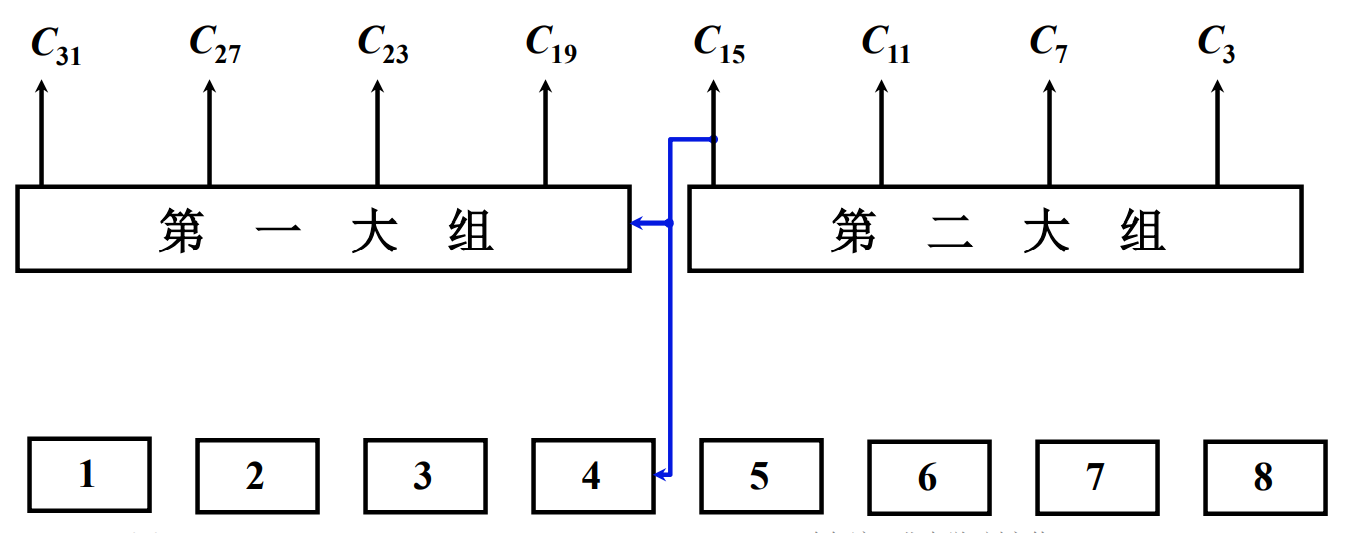

2. 双重分组跳跃进位链

特征:n 位全加器分若干大组,大组中又包含若干 小组。每个大组中小组的最高位进位同时产生。 大组与大组之间采用串行进位。以 n = 32 n=32 n=32为例:

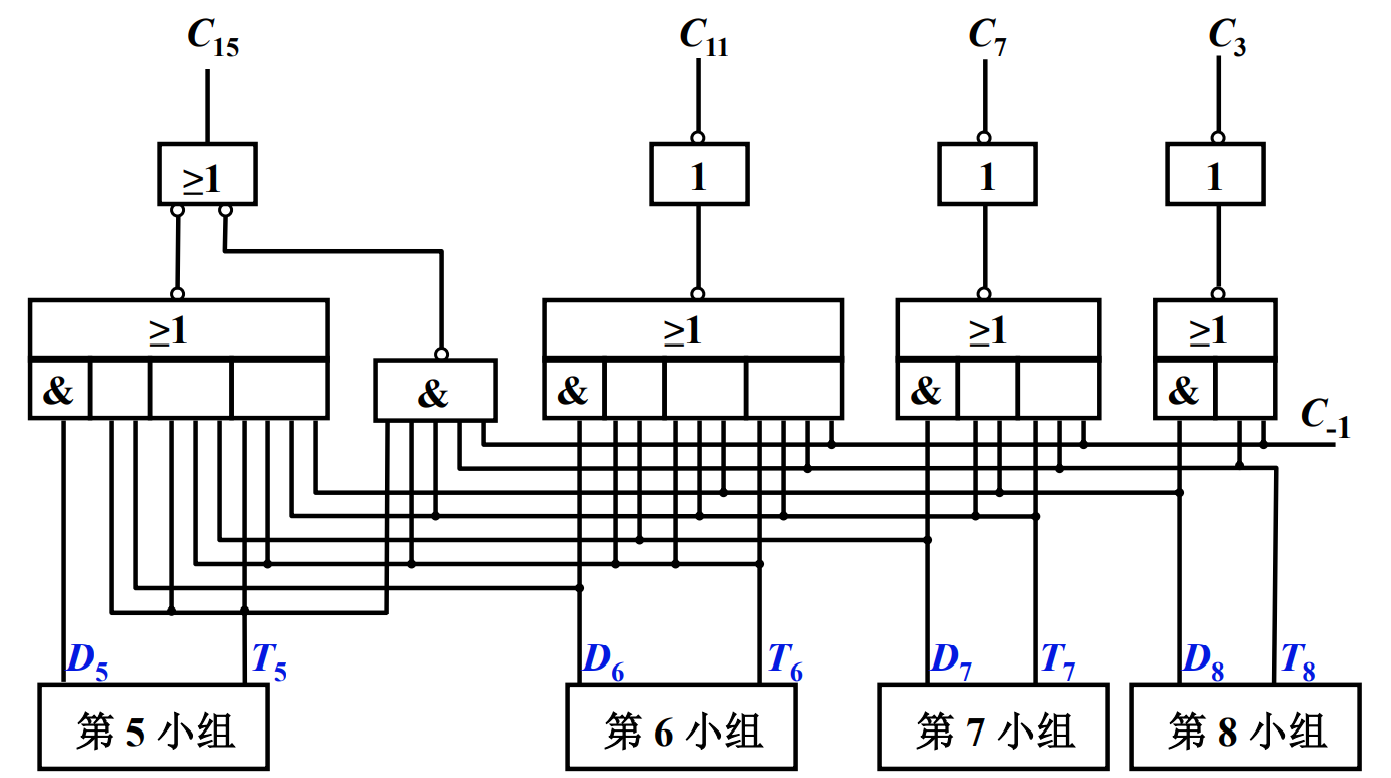

1. 大组进位分析

以第二大组为例:

C 3 = d 3 + t 3 C 2 = d 3 + t 3 d 2 + t 3 t 2 d 1 + t 3 t 2 t 1 d 0 ⏞ D 8 + t 3 t 2 t 1 t 0 ⏞ T 8 C − 1 同 理 有 : { C 7 = D 7 + T 7 C 3 C 11 = D 6 + T 6 C 7 C 15 = D 5 + T 5 C 11 进 一 步 展 开 可 得 : { C 3 = D 8 + T 8 C − 1 C 7 = D 7 + T 7 C 3 = D 7 + T 7 D 8 + T 7 T 8 C − 1 C 11 = D 6 + T 6 C 7 = D 6 + T 6 D 7 + T 6 T 7 D 8 + T 6 T 7 T 8 C − 1 C 15 = D 5 + T 5 C 11 = D 5 + T 5 D 6 + T 5 T 6 D 7 + T 5 T 6 T 7 D 8 + T 5 T 6 T 7 T 8 C − 1 \begin{aligned} C_3 &= d_3+t_3C_2 \\ &= \overbrace{d_3+t_3d_2+t_3t_2d_1+t_3t_2t_1d_0}^{D_8}+\overbrace{t_3t_2t_1t_0}^{T_8}C_{-1} \end{aligned} \\ 同理有:\\ \begin{cases} C_7 = D_7+T_7C_3 \\ C_{11} = D_6+T_6C_7 \\ C_{15} = D_5+T_5C_{11} \end{cases} \\ 进一步展开可得: \\ \begin{cases} C_3 = D_8+T_8C_{-1} \\ C_7 = D_7+T_7C_3 = D_7+T_7D_8+T_7T_8C_{-1} \\ C_{11} = D_6+T_6C_7 = D_6+T_6D_7+T_6T_7D_8+T_6T_7T_8C_{-1} \\ C_{15} = D_5+T_5C_{11} = D_5+T_5D_6+T_5T_6D_7+T_5T_6T_7D_8+T_5T_6T_7T_8C_{-1} \end{cases} C3=d3+t3C2=d3+t3d2+t3t2d1+t3t2t1d0 D8+t3t2t1t0 T8C−1同理有:⎩⎪⎨⎪⎧C7=D7+T7C3C11=D6+T6C7C15=D5+T5C11进一步展开可得:⎩⎪⎪⎪⎨⎪⎪⎪⎧C3=D8+T8C−1C7=D7+T7C3=D7+T7D8+T7T8C−1C11=D6+T6C7=D6+T6D7+T6T7D8+T6T7T8C−1C15=D5+T5C11=D5+T5D6+T5T6D7+T5T6T7D8+T5T6T7T8C−1

需要注意到:

- D i D_i Di 小组的本地进位 与外来进位无关,其产生只与A、B有关

- T i T_i Ti 小组的传送条件 与外来进位无关 传递外来进位,其产生只与A、B有关

- C 3 、 C 7 、 C 11 、 C 15 C_3、C_7、C_{11}、C_{15} C3、C7、C11、C15是第二大组内每个小组组内的最高进位

- 由这个线路图可以知道:大组内小组的最高位进位是同时产生的

- 注意观察,这个线路图其实和4位并行加法器进位链是一致的

2. 小组进位分析

以第8小组为例,进位线路如图:

- 只产生 低 3 位 的进位和 本小组的 D 8 、 T 8 D_8、 T_8 D8、T8

3. 总结

- 进位产生特点:

- 一个大组内:

- 各小组最高进位同时产生

- 其他进位也同时产生

- 但:小组内最高进位和其他进位不是同时产生的

- 各大组之间采用串行进位,进位不是同时产生的

- 一个大组内:

- 优点:大组内各小组最高进位同时产生也就意味着:当前一大组的进位传递过来后,本大组的最高进位会立即产生并向前传递,因此进位速度大大提高